Chaining dma descriptor tables – Altera Arria V GZ Avalon-ST User Manual

Page 217

Bit

Field

Description

[15:0]

Write DMA EPLAS

Indicates the number of the last descriptor completed by the write

DMA. For simultaneous DMA read and write transfers, EPLAST

is only supported for the final descriptor in the descriptor table.

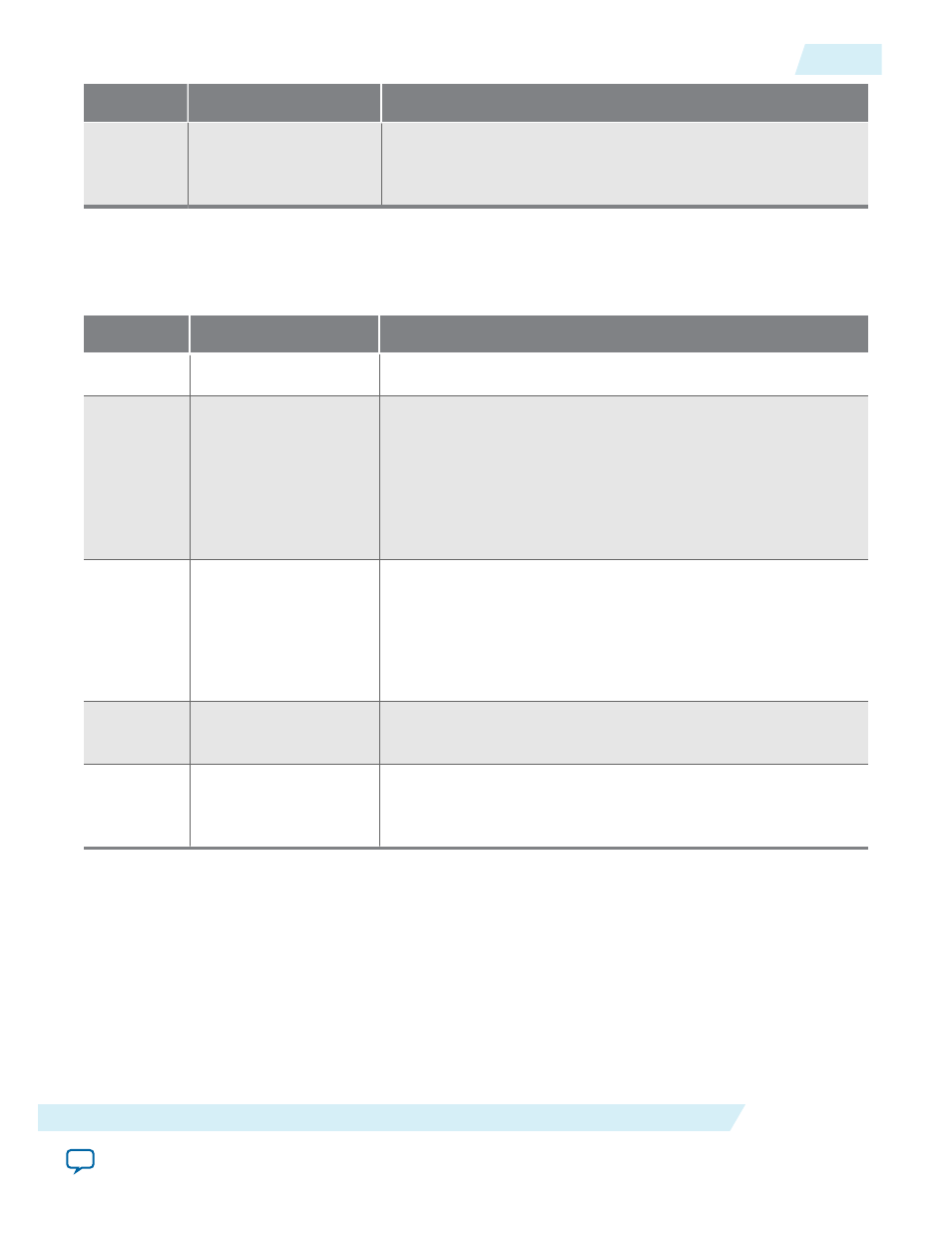

The following table describes the fields in the DMA read status high register. All of these fields are read

only.

Table 17-6: Fields in the DMA Read Status High Register

Bit

Field

Description

[31:24]

Reserved

—

[23:21]

Max Read Request Size

The following encodings are defined:

• 001 128 bytes

• 001 256 bytes

• 010 512 bytes

• 011 1024 bytes

• 100 2048 bytes

[20:17]

Negotiated Link Width

The following encodings are defined:

• 4'b0001 ×1

• 4'b0010 ×2

• 4'b0100 ×4

• 4'b1000 ×8

16

Read DMA Descriptor

FIFO Empty

Indicates that there are no more descriptors pending in the read

DMA.

[15:0]

Read DMA EPLAST

Indicates the number of the last descriptor completed by the read

DMA. For simultaneous DMA read and write transfers, EPLAST

is only supported for the final descriptor in the descriptor table.

Chaining DMA Descriptor Tables

The following table describes the Chaining DMA descriptor table. This table is stored in the BFM shared

memory. It consists of a four-dword descriptor header and a contiguous list of <n> four-dword descrip‐

tors. The Endpoint chaining DMA application accesses the Chaining DMA descriptor table for two

reasons:

• To iteratively retrieve four-dword descriptors to start a DMA

• To send update status to the RP, for example to record the number of descriptors completed to the

descriptor header

UG-01127_avst

2014.12.15

Chaining DMA Descriptor Tables

17-13

Testbench and Design Example

Altera Corporation