Altera Arria V GZ Avalon-ST User Manual

Page 17

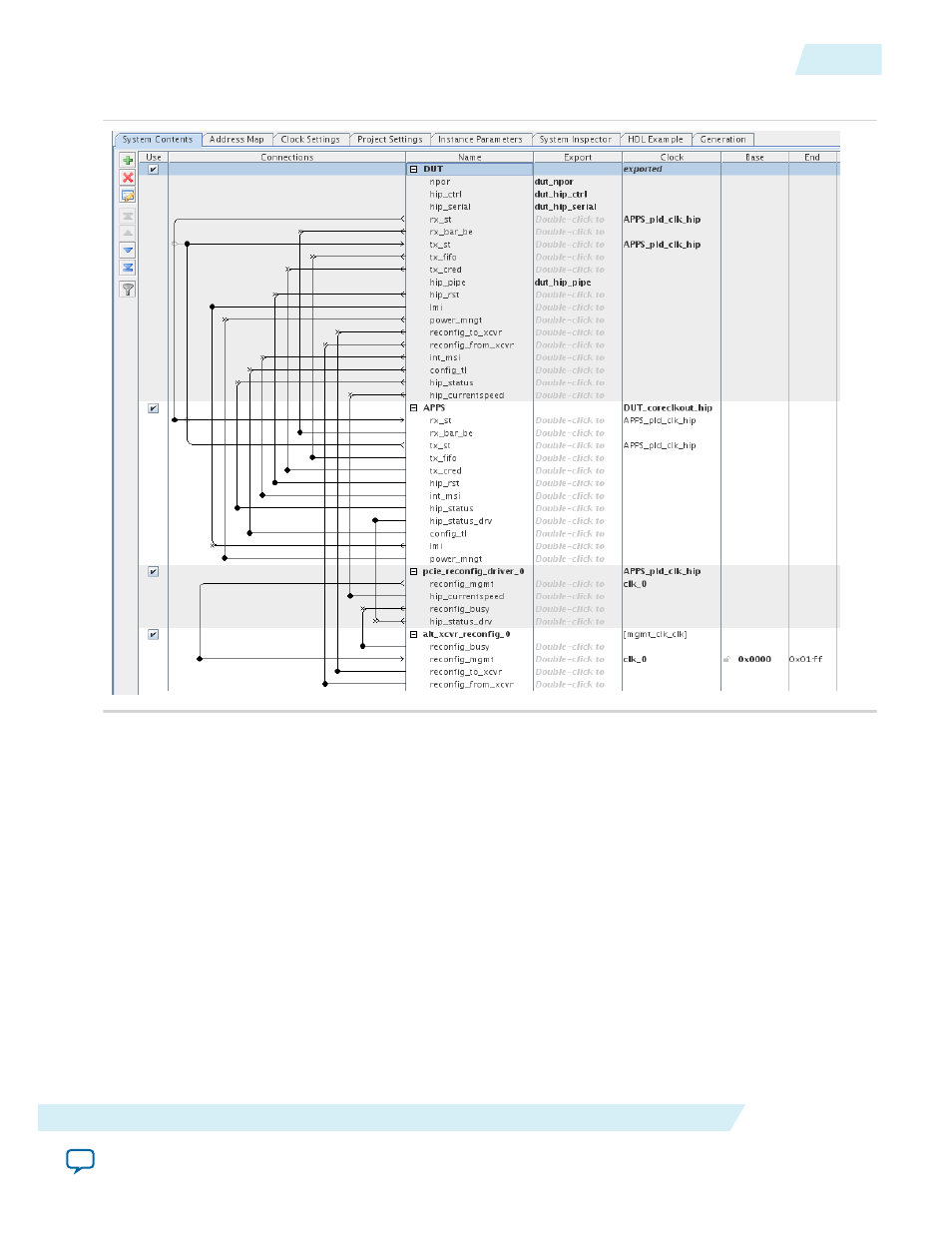

Figure 2-2: Complete Gen1 ×8 Endpoint (DUT) Connected to Example Design (APPS)

The example design includes the following components:

• DUT—This is Gen1 ×8 Endpoint. For your own design, you can select the data rate, number of lanes,

and either Endpoint or Root Port mode.

• APPS—This Root Port BFM configures the DUT and drives read and write TLPs to test DUT

functionality. An Endpoint BFM is available if your PCI Express design implements a Root Port.

• pcie_reconfig_driver_0—This Avalon-MM master drives the Transceiver Reconfiguration Controller.

The pcie_reconfig_driver_0 is implemented in clear text that you can modify if your design requires

different reconfiguration functions. After you generate your Qsys system, the Verilog HDL for this

component is available as:

<working_dir>/<variant_name>/testbench/<variant_name>_tb/simulation/

submodules/altpcie_reconfig_driver.sv

.

• Transceiver Reconfiguration Controller—The Transceiver Reconfiguration Controller dynamically

reconfigures analog settings to improve signal quality. For Gen1 and Gen2 data rates, the Transceiver

Reconfiguration Controller must perform offset cancellation and PLL calibration. For the Gen3 data

rate, the pcie_reconfig_driver_0 performs AEQ through the Transceiver Reconfiguration Controller.

UG-01127_avst

2014.12.15

Qsys Design Flow

2-3

Getting Started with the Arria V GZ Hard IP for PCI Express

Altera Corporation