Signals, Signals –14, Ht link rx signals – Altera HyperTransport MegaCore Function User Manual

Page 40: Ht link system signals, Ht link tx signals

3–14

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

Signals

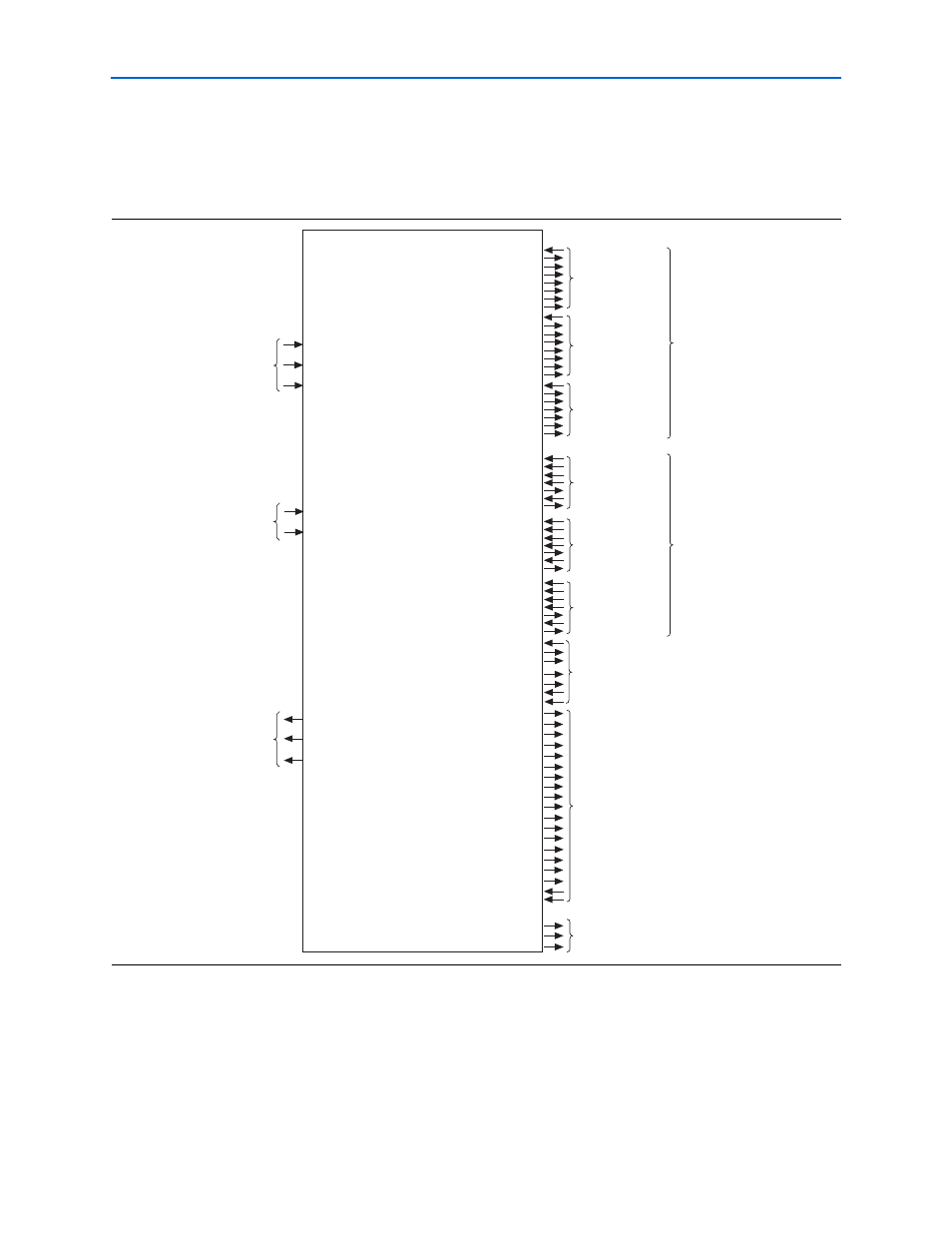

shows a top-level view of the HyperTransport MegaCore function interface

signals.

The HT interface signals are also external I/O pins on the chip. Each HT interface

signal is in one of the following groups:

■

HT link Rx signals

■

HT link system signals

■

HT link Tx signals

Figure 3–9. Top-Level HyperTransport MegaCore Function Sign

HyperTransport M egaCore Function

RxCAD_i[7:0]

RxCTL_i

RxClk_i

TxCAD_o[7:0]

TxCTL_o

TxClk_o

PwrOk

Rstn

RxNpDat_o[63:0]

RxNpVal_o

RxNpDav_o

RxNpEna_i

TxREop_i

Rx Non-Posted

Command/Data

Buffer Interface

Rx Posted

Command/Data

Buffer Interface

Rx Response

Command/Data

Buffer Interface

Tx Non-Posted

Command/Data

Buffer Interface

Tx Posted

Command/Data

Buffer Interface

Tx Response

Command/Data

Buffer Interface

HT Link

Rx Signals

HT Link

System

Signals

HT Link

Tx Signals

Rx Interface

Tx Interface

TxPDat_i[63:0]

TxPMty_i[2:0]

TxPDav_o

TxPSop_i

TxPDatEna_i

TxPEop_i

TxPWrRjct_o

TxRDat_i[63:0]

TxRMty_i[2:0]

TxRDav_o

TxRSop_i

TxRDatEna_i

TxNpDat_i[63:0]

TxNpMty_i[2:0]

TxNpDav_o

TxNpSop_i

TxNpDatEna_i

TxNpEop_i

TxNpWrRjct_o

TxRWrRjct_o

CsrCmdReg_o[15:0]

CsrStatReg_o[15:0]

CsrCapCmdReg_o[15:0]

CsrCapLnk0CtrlReg_o[15:0]

CsrCapLnk1CtrlReg_o[15:0]

CsrCapLnk0CfgReg_o[15:0]

CsrCapLnk1CfgReg_o[15:0]

CsrCapFtrReg_o[7:0]

CsrCapLnk0ErrReg_o[3:0]

CsrCapLnk1ErrReg_o[3:0]

CsrCapErrHndlngReg_o[15:0]

CSR Module Signals

RxNpCmdBarHit_o[2:0]

RxNpEop_o

RxNpSop_o

RxNpMty_o[2:0]

RxPDat_o[63:0]

RxPVal_o

RxPDav_o

RxPEna_i

RxPCmdBarHit_o[2:0]

RxPEop_o

RxPSop_o

RxPMty_o[2:0]

RxRDat_o[63:0]

RxRVal_o

RxRDav_o

RxREna_i

RxREop_o

RxRSop_o

RxRMty_o[2:0]

RespErr

SignaledTabrt

Bar0Reg_o[31:0]

Bar1Reg_o[31:0]

Bar2Reg_o[31:0]

Bar3Reg_o[31:0]

Bar4Reg_o[31:0]

Bar5Reg_o[31:0]

ClmdRCmdBufOvrFlw Err_o

ClmdNPCmdBufOvrFlw Err_o

ClmdPCmdBufOvrFlw Err_o

Buffer Overflow

Indicator Signals

RefClk

RxLnkClkD4

RefClkWrmRst

RefClkCldRst

System Signals

RxLnkClkD4Locked_o

TxPllAreset_i

RxPllAreset_i