Altera HyperTransport MegaCore Function User Manual

Page 47

Chapter 3: Specifications

3–21

HyperTransport MegaCore Function Specification

© November 2009

Altera Corporation

HyperTransport MegaCore Function User Guide

Preliminary

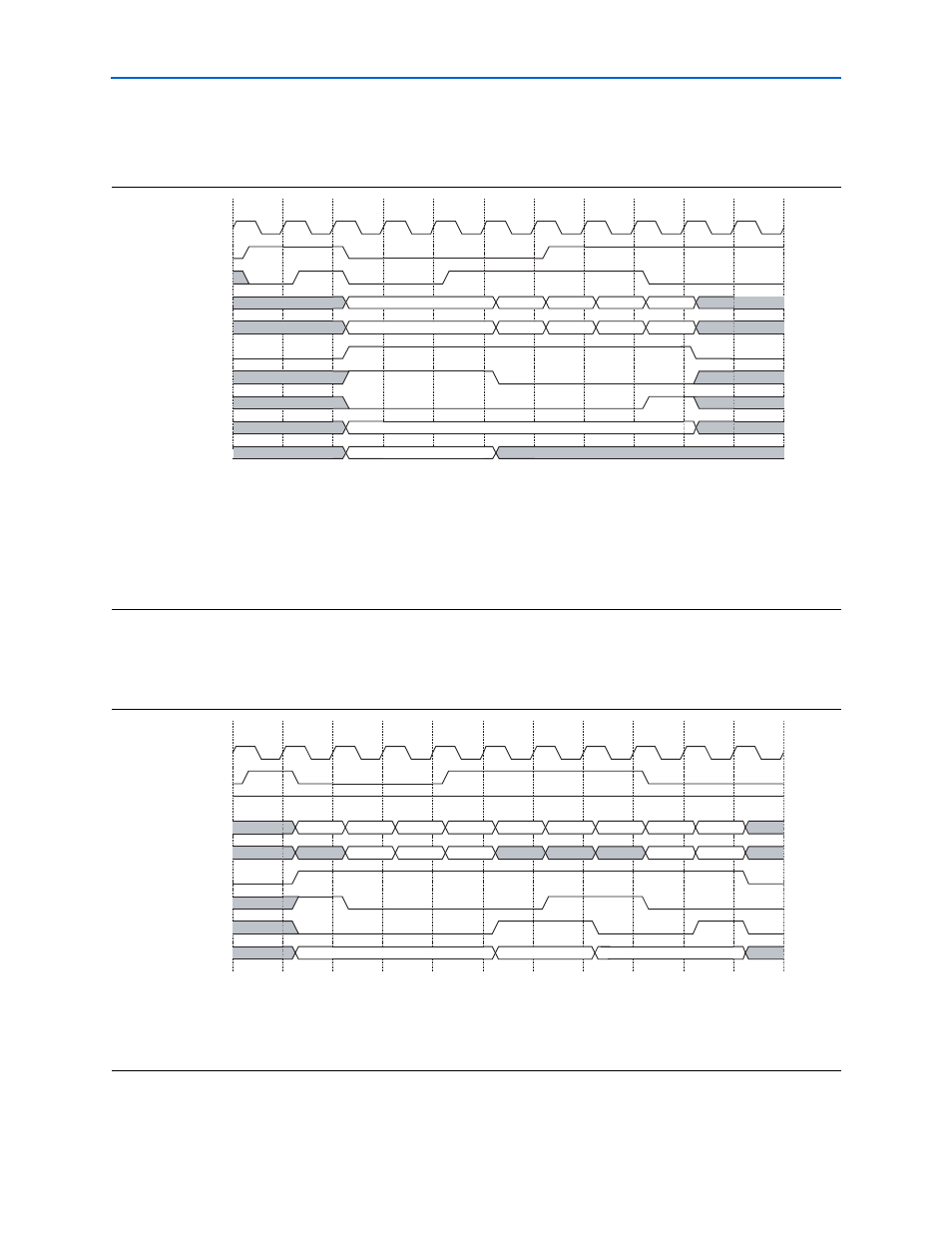

shows a 32-byte write interrupted with user-inserted wait states the clock

cycle after the command

Sop_o = 1

is asserted.

shows a 38-byte read response, target done, and 16-byte read response

transferred back to back across the Rx interface with no delays.

Figure 3–12. 32-Byte Write with User-Inserted Wait States across Rx Interface Timing Diagram

Notes to

:

(1)

Dav_o

is shown to deassert initially, indicating that the Rx buffer does not have any additional packets stored beyond the one that is currently

being read.

(2) The user-side logic deasserts

Ena_i

to insert a wait state (for example to decode a command).

(3)

Ena_i

is low at this time so that the next command (indicated by

Dav_o

) is held off.

(4) Outputs are still valid, the user must qualify them with the previous

Ena_i

to determine if it is new data.

(5)

BarHit_o

is valid while

Val_o

and

Sop_o

are asserted.

2

3

4

5

6

7

9

10

RefClk

Dav_o

8

1

Ena_i

Dat_o[31:0]

Dat_o[63:32]

Val_o

Sop_o

Eop_o

Mty_o[2:0]

11

DW0

DW2

DW4

DW6

DW1

DW3

DW6

DW7

0b000

Addr[39:8]

(4)

Write

(4)

(2)

(3)

(4)

(4)

BarHit_o[2:0]

Matching Bar (4)

(1)

Figure 3–13. Streaming Responses Transferred across Rx Interface Timing Diagram

Notes to

:

(1)

Dat_o[63:32]

is not valid during this time because the command is only a 4-byte read response.

(2)

Dat_o[63:32]

is not valid during this time because the response is only seven double words long.

(3)

Dat_o[63:32]

is not valid during this time because the command is only a 4-byte target done.

2

3

4

5

6

7

9

10

RefClk

Dav_o

8

1

Ena_i

Dat_o[31:0]

Dat_o[63:32]

Val_o

Sop_o

Eop_o

Mty_o[2:0]

11

RdResp

DW0

DW2

DW4

DW6

DW1

DW3

DW5

(1)

(2)

0b000

0b100

(1)

(3)

TgtDone

RdResp

DWa

DWb

DWc

DWd

0b000