Base address registers – Altera HyperTransport MegaCore Function User Manual

Page 68

A–2

Appendix A: Parameters

Parameter Lists

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

Base Address Registers

lists the parameters modified by settings on the Base Address Registers tab

of the IP Toolbench wizard.

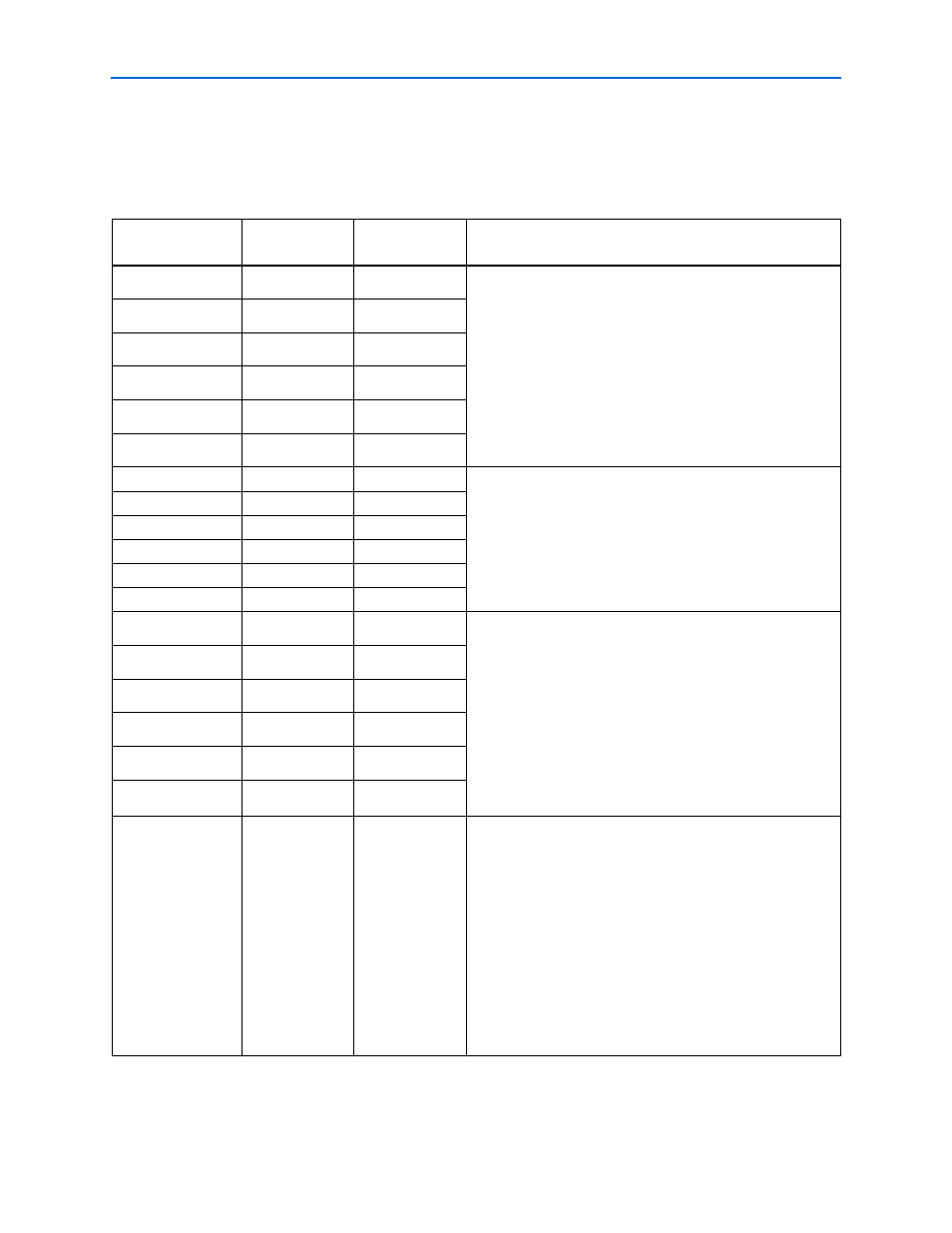

Table A–2. BAR Parameters

Parameter

Default

Available

Setting(s)

Description

Bar0AndMask

0xFFF0_0000

Any 32-bit value

The AndMask defines the writable bits of the specified BAR.

For 32 bit memory space BARs, only bits 31-10 can be

writable, i.e., the minimum decodable memory space is

1KBytes. Only BAR1, BAR3, and BAR5 can be the upper BARs

of a 64 bit BAR. In this case, all bits can be writable.

Bar1AndMask

0x0

Any 32-bit value

Bar2AndMask

0x0

Any 32-bit value

Bar3AndMask

0x0

Any 32-bit value

Bar4AndMask

0x0

Any 32-bit value

Bar5AndMask

0x0

Any 32-bit value

Bar0MatchMask

0xFFF0_0000

Any 32-bit value

The MatchMask specifies which bits of the specified BAR

should be used for matching addresses. In all cases, the

MatchMask should be identical to the AndMask.

Bar1MatchMask

0x0

Any 32-bit value

Bar2MatchMask

0x0

Any 32 -bit value

Bar3MatchMask

0x0

Any 32-bit value

Bar4MatchMask

0x0

Any 32-bit value

Bar5MatchMask

0x0

Any 32-bit value

Bar0OrMask

0x8

Any 4-bit value

The OrMask specifies which low-order type bits of the BAR

should be set to 1.

■

Bit[0] – I/O space

■

Bit[1] – Reserved

■

Bit[2] – 64 bit BAR (only valid on BAR0, BAR2, and BAR4)

Only valid when Bit [0]=0

■

Bit[3] – Prefetchable

On the upper BAR of a 64 bit BAR, all of these bits must be 0.

Bar1OrMask

0x0

Any 4-bit value

Bar2OrMask

0x0

Any 4-bit value

Bar3OrMask

0x0

Any 4-bit value

Bar4OrMask

0x0

Any 4-bit value

Bar5OrMask

0x0

Any 4-bit value

CLAIM_COMPAT

0x0

0 or 1

Compatibility Request Claiming occurs based on whether the

CLAIM_COMPAT parameter is set to zero or 1. When the value

of this parameter is zero, the HyperTransport MegaCore

function does not claim Read and Write requests that have the

Compat bit set to 1, posted requests are ignored and

nonposted requests have a NXA error response returned.

When the CLAIM_COMPAT parameter is set to the value 1, the

requests are claimed and presented on the Rx user interfaces

of the function. Setting the value to 1 can be used to

implement an x86 Subtractive Decode device. The

CLAIM_COMPAT parameter is set by the Claim All Read And

Write Requests With Compat Bit Equal To '1' box on the Base

Address Registers tab.