Altera HyperTransport MegaCore Function User Manual

Page 60

3–34

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

Subsystem Vendor ID, Subsystem ID (Offset 0x2C)

The subsystem vendor ID and subsystem ID are read-only as defined in the PCI

specification. They are parameters in the HyperTransport MegaCore function.

Capabilities Pointer (Actual Offset 0x34)

This register is read-only register for the HyperTransport MegaCore function. It

points to 0x40 in the HyperTransport MegaCore function.

HT Capabilities Block

The HyperTransport MegaCore function uses a slave/primary interface capabilities

block format as defined in the HT specification.

shows this block format.

Capabilities ID (Actual Offset 0x40)

This register is read only as defined by the HT specification and is hardwired to 0x08.

Capabilities Pointer (Actual Offset 0x41)

This register is read only as defined by the HT specification. In the HyperTransport

MegaCore function, it is hardwired to 0x00, indicating no additional capability blocks.

HT Capability Command Register (Actual Offset 0x42)

describes the HT capability command register.

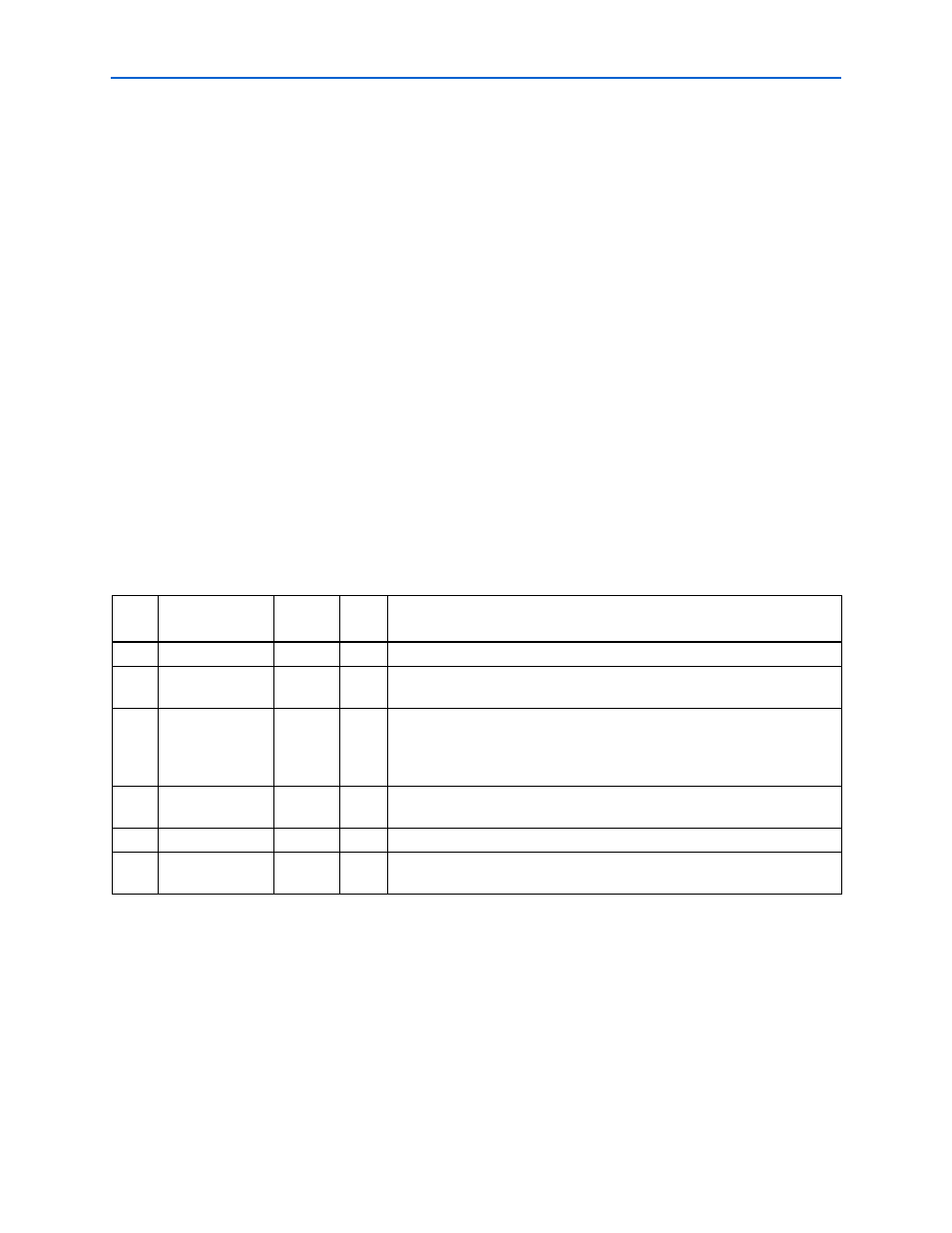

Table 3–16. HT Capability Command Register Offset: Capability Pointer + 0x02 (Actual Offset: 0x42)

Bits

Name

Register

Type

Reset

Used

Description

4:0

Base Unit ID

R/W

Warm Indicates the lowest number UnitID belonging to the device.

9:5

Unit Count

R/O

N/A

Number of UnitID occupied by this device. The MegaCore function does not

occupy more than one UnitID.

10

Master Host

R/O

N/A

Because a device can have up to two links (link 0, link 1) this bit indicates

which one links to the host bridge. The HyperTransport MegaCore function

hardwires this bit to 0 to indicate that link 0 is always connected to the host

bridge. Additionally, the CSR module can only be accessed via link 0.

11

Default Direction

R/O

N/A

Indicates which directions to which the request should be sent. This bit is

hardwired to 0 to indicate that all requests should be sent to the host bridge.

12

Drop on Uninit

R/W

Cold

Drop on uninitialized link. See

for details.

15:13 Capabilities Type

R/O

N/A

Indicates the type of capabilities. This register is hardwired to 000 to

indicate that the capabilities type is slave/primary.

Notes: to

(1) This register is defined as a read/write in the HT specification. The HyperTransport MegaCore function does not allow both links in a tunnel to

write to the CSR. Therefore, this bit is always hardwired to 0 to indicate that link 0 is the one connected to the host bridge.

(2) This bit is defined as Read/Write in the HT specification so that the direction is programmable. The HyperTransport MegaCore function only

supports one direction.

(3) This bit determines what happens to packets loaded in the transmitter while init complete and end chain bits are cleared. Refer to the

HyperTransport I/O Link Specification Revision 1.03 for a description of this functionality.