Altera HyperTransport MegaCore Function User Manual

Page 56

3–30

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

During normal operation of the HyperTransport link, clocks may change from the

initial 200 MHz frequency to a faster frequency. If the

RxClk_i

input to the function

stops during this change, the Rx PLL must be reset. The HyperTransport interface

does not provide sufficient indication to directly generate the PLL reset for this

situation. However, a Verilog HDL reference design that generates the

HyperTransport Rx PLL reset at the appropriate time is installed with the

HyperTransport MegaCore function.

f

The Verilog HDL reference design code that generates the HT Rx PLL reset at the

appropriate time can be found in your Altera MegaCore IP library installation at

<path>/ht/example/pll_reset/ht_with_pll_reset.v

The

RxPllAreset_i

and

TxPllAreset_i

inputs can be tied low to provide the

PLL behavior that was present in HyperTransport MegaCore function v1.3.0 and

earlier.

CSR Interface Signals

All required status information in the CSR module is provided to the local side

through the signals shown in

.

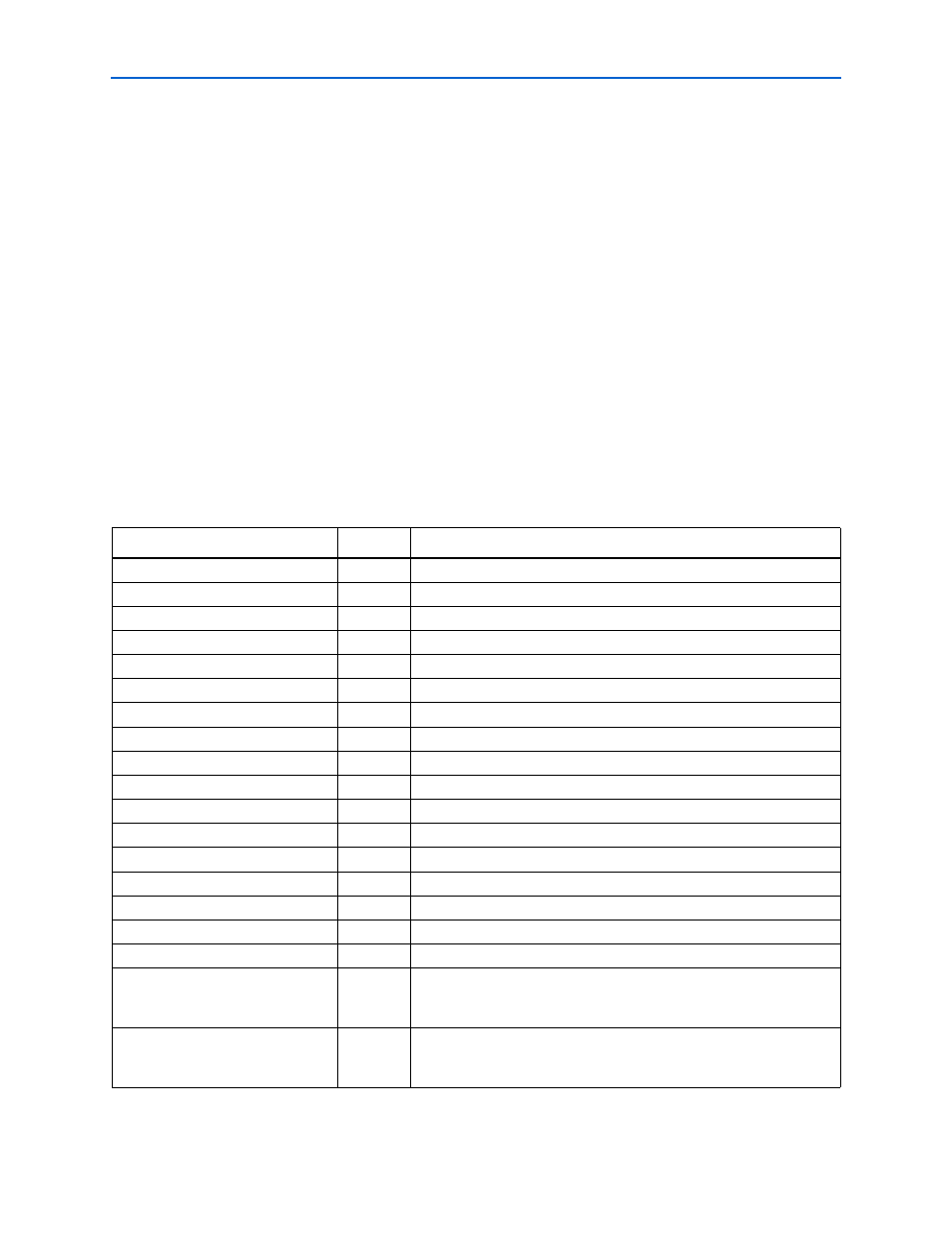

Table 3–10. CSR Interface Signals

Signal Name

Direction

Description

CsrCmdReg[15:0]

Output

Command register.

CsrStatReg[15:0]

Output

Status register.

CsrCapReg[15:0]

Output

Capability command register.

CsrCapLnk0CtrlReg[15:0]

Output

Capability link 0 control register.

CsrCapLnk1CtrlReg[15:0]

Output

Capability link 1 control register.

CsrCapLnk0CfgReg[15:0]

Output

Capability link 0 configuration register.

CsrCapLnk1CfgReg[15:0]

Output

Capability link 1 configuration register.

CsrCapFtrReg[7:0]

Output

Capability feature register.

CsrCapLnk0ErrReg[3:0]

Output

Capability link 0 error register.

CsrCapLnk1ErrReg[3:0]

Output

Capability link 1 error register.

CsrCapErrHndlngReg[15:0]

Output

Capability error handling register.

Bar0Reg[31:0]

Output

Base address register 0.

Bar1Reg[31:0]

Output

Base address register 1.

Bar2Reg[31:0]

Output

Base address register 2.

Bar3Reg[31:0]

Output

Base address register 3.

Bar4Reg[31:0]

Output

Base address register 4.

Bar5Reg[31:0]

Output

Base address register 5.

RespErr

Input

The user application logic asserts this signal to indicate that an

unexpected response was received. Asserting this signal causes the

appropriate CSR bit to be set.

SignaledTabrt

Input

The user application logic asserts this signal to indicate that a target

abort was signaled (the target issued a response with a non-NXA error).

Asserting this signal causes the appropriate CSR bit to be set.