Csr module, Csr module –31 – Altera HyperTransport MegaCore Function User Manual

Page 57

Chapter 3: Specifications

3–31

HyperTransport MegaCore Function Specification

© November 2009

Altera Corporation

HyperTransport MegaCore Function User Guide

Preliminary

Buffer Overflow Indicator Signals

describes the buffer overflow indicator signals. When an a Rx buffer

overflows due to a failure in the HyperTransport link flow control mechanism, the

overflow error bit is set in the CSR HT capability link error 0 register. These signals

indicate which virtual channel buffer had the overflow. These signals are most useful

in simulation and typically do not need to be connected in the user design.

CSR Module

The CSR module contains all of the configuration space registers and handles write

requests, read requests and response accesses to the CSR space.

show the full CSR register map.

capabilities block format.

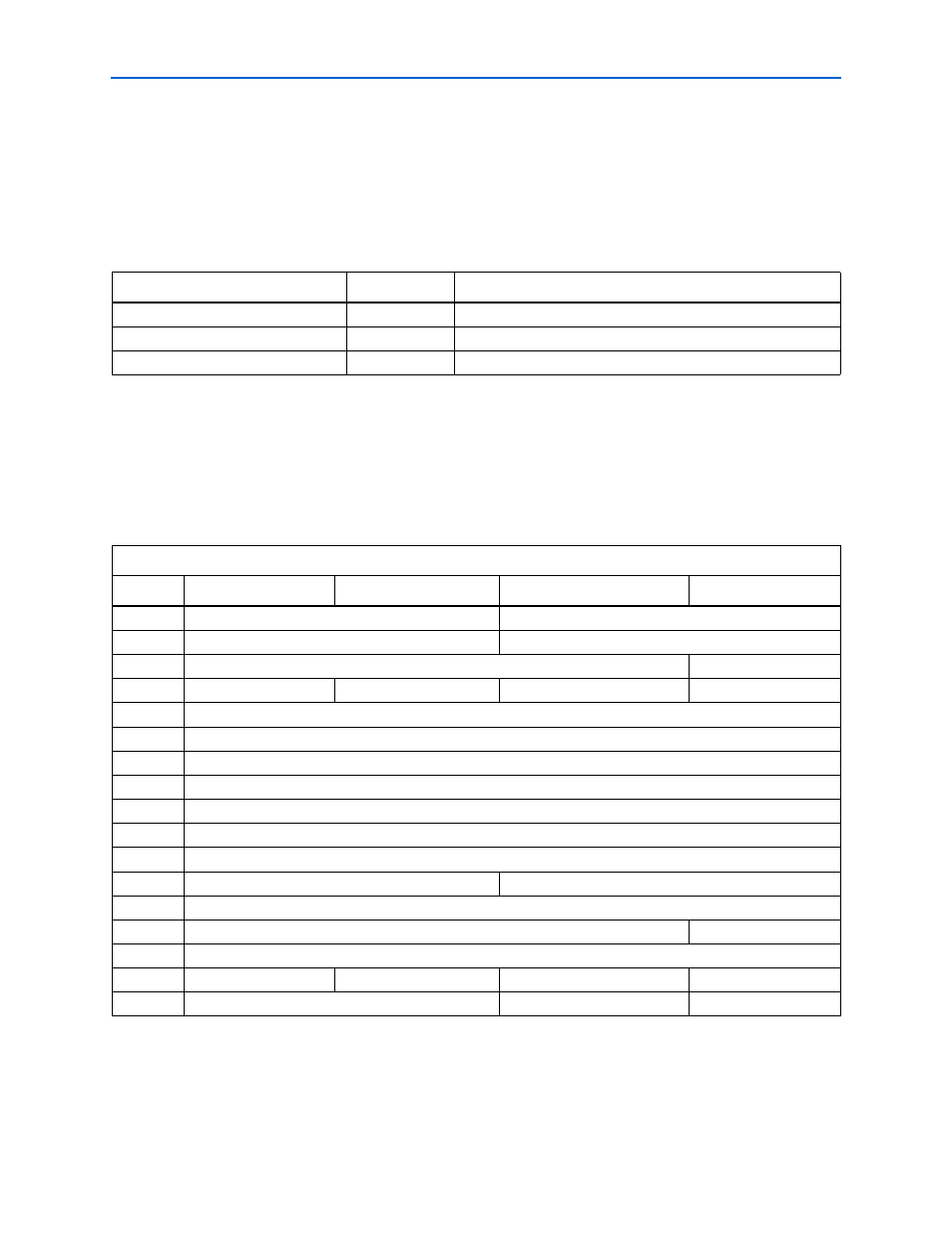

Table 3–11. Buffer Overflow Indicator Signals

Signal Name

Direction

Description

ClmdRCmdBufOvrFlw_Err_o

Output

Rx Response Command/Data buffer overflow.

ClmdPCmdBufOvrFlw_Err_o

Output

Rx Posted Command/Data buffer overflow.

ClmdNpCmdBufOvrFlw_Err_o

Output

Rx Non-Posted Command/Data buffer overflow.

Table 3–12. CSR Register Map Without Primary Interface Capabilities Block

Hyper Transport Technology Device Header

Address

Byte 3

Byte 2

Byte1

Byte 0

00

Device ID

Vendor ID

04

Command

08

Revision ID

0C

Latency Timer

Cache Line

10

14

18

1C

20

24

28

CardBus CIS Pointer

2C

Subsystem ID

Subsystem Vendor ID

30

Expansion ROM Base Address

34

Reserved

Capabilities Pointer

38

Reserved

3C

Interrupt Pin

Interrupt Line

+18

Reserved

Mem Limit Upper

Mem Base Upper

Notes to

:

(1) The configuration register is not used by the HT specification. The register is a read-only register, and Read returns 0s.

(2) The register is not supported in the HyperTransport MegaCore function. The register is a read-only register and Read returns 0s.

(3) The register is a read-only register in the HyperTransport MegaCore function.

(4) The register is read/write in the HyperTransport MegaCore function.