I/o resources, Max v cpld 5m2210 system controller, I/o resources –5 – Altera Cyclone V E FPGA Development Board User Manual

Page 13: Max v cpld 5m2210 system controller –5

Chapter 2: Board Components

2–5

MAX V CPLD 5M2210 System Controller

March 2013

Altera Corporation

Cyclone V E FPGA Development Board

Reference Manual

I/O Resources

The Cyclone V E FPGA 5CEFA7F31I7N device has total of 480 user I/Os.

lists the Cyclone V E FPGA I/O pin count and usage by function on the board.

MAX V CPLD 5M2210 System Controller

The board utilizes the 5M2210 System Controller, an Altera MAX V CPLD, for the

following purposes:

■

FPGA configuration from flash

■

Power measurement

■

Control and status registers for remote system update

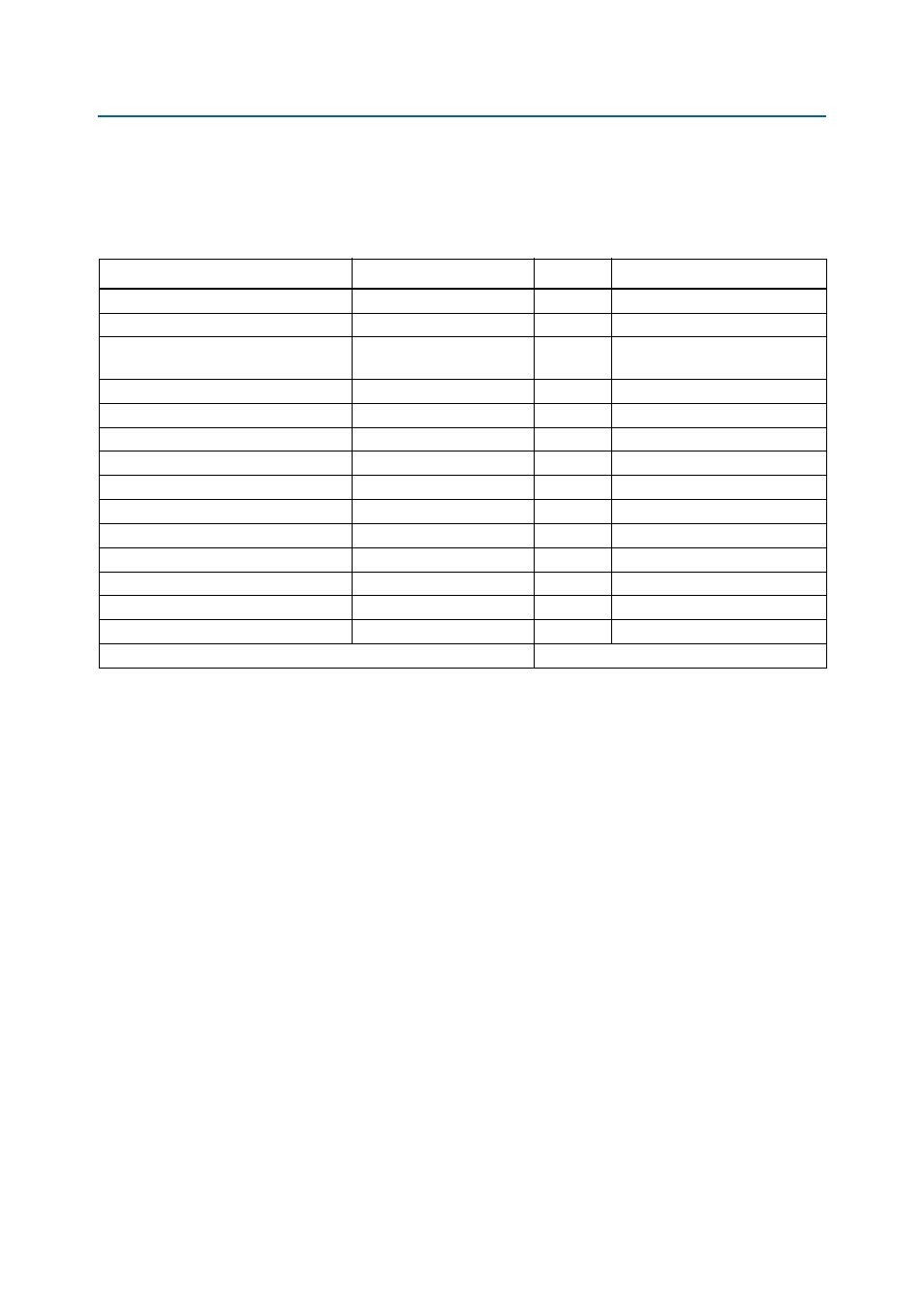

Table 2–3. Cyclone V E FPGA I/O Pin Count

Function

I/O Standard

I/O Count

Special Pins

DDR3

1.5-V SSTL

71

One differential x4 DQS pin

LPDDR2

1.2-V HSUL

37

One differential x2 DQS pin

Flash, SSRAM, EEPROM, and MAX V

FSM bus

2.5-V CMOS, 3.3-V LVCMOS

69

—

HSMC port

2.5-V CMOS + LVDS

79

17 LVDS, I

2

C

Gigabit Ethernet port

2.5-V CMOS

42

—

Embedded USB-Blaster II

2.5-V CMOS

20

—

Debug Header

1.5-V, 2.5-V

20

—

UART

3.3-V LVTTL

4

—

USB-UART

2.5-V CMOS

12

—

Push buttons

2.5-V CMOS

5

One DEV_CLRn pin

DIP switches

2.5-V CMOS

4

—

Character LCD

2.5-V CMOS

11

—

LEDs

2.5-V CMOS

9

—

Clock or Oscillators

2.5-V CMOS + LVDS

12

One clock out pin

Total I/O Used:

395