Altera Cyclone V E FPGA Development Board User Manual

Page 37

Chapter 2: Board Components

2–29

Components and Interfaces

March 2013

Altera Corporation

Cyclone V E FPGA Development Board

Reference Manual

72

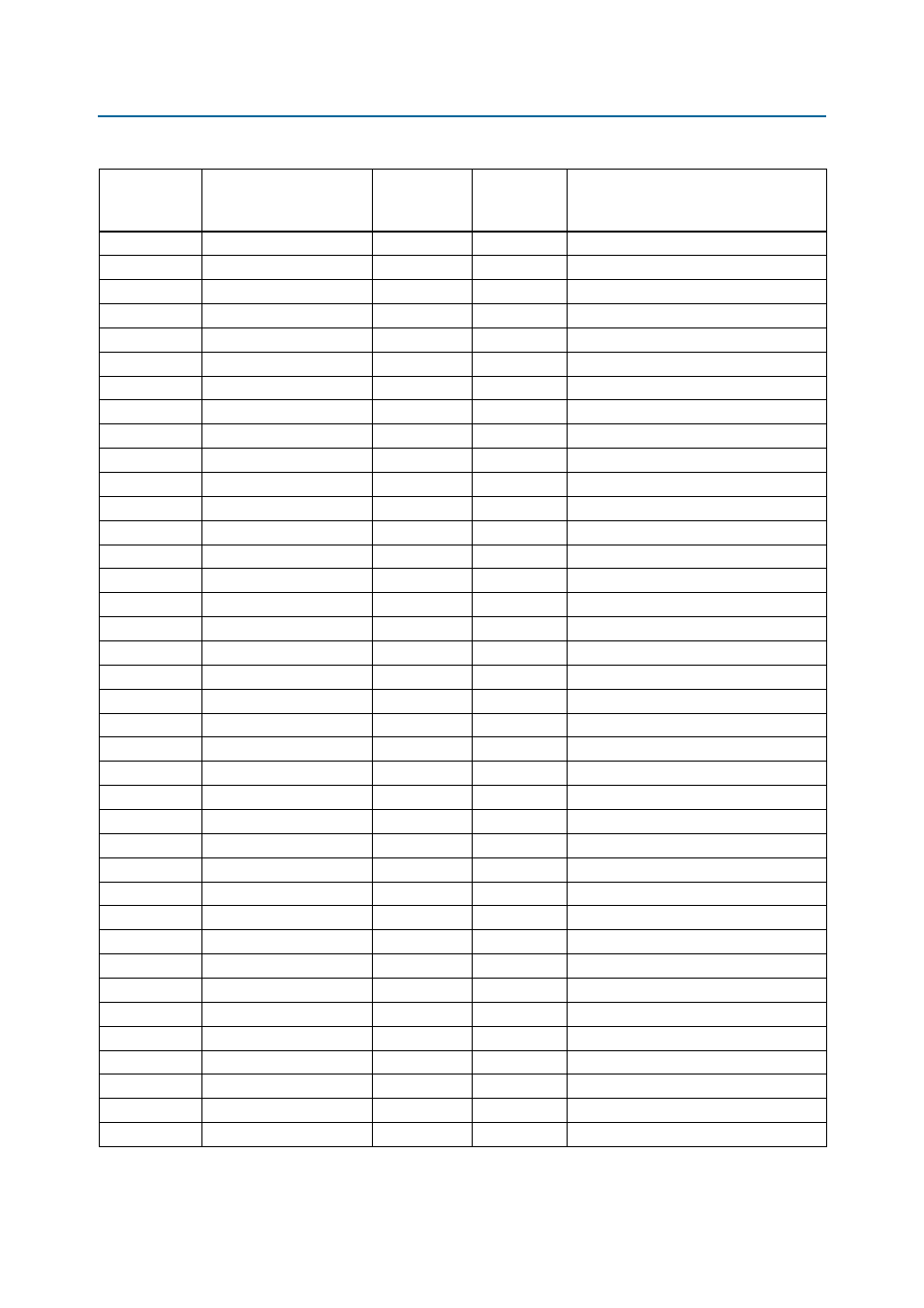

HSMC_RX_D_P4

AA21

LVDS or 2.5-V LVDS RX bit 4 or CMOS bit 21

73

HSMC_TX_D_N4

AJ24

LVDS or 2.5-V LVDS TX bit 4n or CMOS bit 22

74

HSMC_RX_D_N4

AB21

LVDS or 2.5-V LVDS RX bit 4n or CMOS bit 23

77

HSMC_TX_D_P5

AH21

LVDS or 2.5-V LVDS TX bit 5 or CMOS bit 24

78

HSMC_RX_D_P5

AB19

LVDS or 2.5-V LVDS RX bit 5 or CMOS bit 25

79

HSMC_TX_D_N5

AJ22

LVDS or 2.5-V LVDS TX bit 5n or CMOS bit 26

80

HSMC_RX_D_N5

AC19

LVDS or 2.5-V LVDS RX bit 5n or CMOS bit 27

83

HSMC_TX_D_P6

AJ23

LVDS or 2.5-V LVDS TX bit 6 or CMOS bit 28

84

HSMC_RX_D_P6

AC21

LVDS or 2.5-V LVDS RX bit 6 or CMOS bit 29

85

HSMC_TX_D_N6

AK23

LVDS or 2.5-V LVDS TX bit 6n or CMOS bit 30

86

HSMC_RX_D_N6

AD20

LVDS or 2.5-V LVDS RX bit 6n or CMOS bit 31

89

HSMC_TX_D_P7

AK21

LVDS or 2.5-V LVDS TX bit 7 or CMOS bit 32

90

HSMC_RX_D_P7

AD19

LVDS or 2.5-V LVDS RX bit 7 or CMOS bit 33

91

HSMC_TX_D_N7

AK22

LVDS or 2.5-V LVDS TX bit 7n or CMOS bit 34

92

HSMC_RX_D_N7

AE20

LVDS or 2.5-V LVDS RX bit 7n or CMOS bit 35

95

HSMC_CLK_OUT_P1

AE22

LVDS or 2.5-V LVDS or CMOS clock out 1 or CMOS bit 36

96

HSMC_CLK_IN_P1

AB14

LVDS or 2.5-V LVDS or CMOS clock in 1 or CMOS bit 37

97

HSMC_CLK_OUT_N1

AF23

LVDS or 2.5-V LVDS or CMOS clock out 1 or CMOS bit 38

98

HSMC_CLK_IN_N1

AC14

LVDS or 2.5-V LVDS or CMOS clock in 1 or CMOS bit 39

101

HSMC_TX_D_P8

AJ20

LVDS or 2.5-V LVDS TX bit 8 or CMOS bit 40

102

HSMC_RX_D_P8

AF21

LVDS or 2.5-V LVDS RX bit 8 or CMOS bit 41

103

HSMC_TX_D_N8

AK20

LVDS or 2.5-V LVDS TX bit 8n or CMOS bit 42

104

HSMC_RX_D_N8

AG22

LVDS or 2.5-V LVDS RX bit 8n or CMOS bit 43

107

HSMC_TX_D_P9

AJ19

LVDS or 2.5-V LVDS TX bit 9 or CMOS bit 44

108

HSMC_RX_D_P9

AF20

LVDS or 2.5-V LVDS RX bit 9 or CMOS bit 45

109

HSMC_TX_D_N9

AK18

LVDS or 2.5-V LVDS TX bit 9n or CMOS bit 46

110

HSMC_RX_D_N9

AG21

LVDS or 2.5-V LVDS RX bit 9n or CMOS bit 47

113

HSMC_TX_D_P10

AJ17

LVDS or 2.5-V LVDS TX bit 10 or CMOS bit 48

114

HSMC_RX_D_P10

AF18

LVDS or 2.5-V LVDS RX bit 10 or CMOS bit 49

115

HSMC_TX_D_N10

AJ18

LVDS or 2.5-V LVDS TX bit 10n or CMOS bit 50

116

HSMC_RX_D_N10

AF19

LVDS or 2.5-V LVDS RX bit 10n or CMOS bit 51

119

HSMC_TX_D_P11

AK25

LVDS or 2.5-V LVDS TX bit 11 or CMOS bit 52

120

HSMC_RX_D_P11

AG18

LVDS or 2.5-V LVDS RX bit 11 or CMOS bit 53

121

HSMC_TX_D_N11

AG24

LVDS or 2.5-V LVDS TX bit 11n or CMOS bit 54

122

HSMC_RX_D_N11

AG19

LVDS or 2.5-V LVDS RX bit 11n or CMOS bit 55

125

HSMC_TX_D_P12

AH19

LVDS or 2.5-V LVDS TX bit 12 or CMOS bit 56

126

HSMC_RX_D_P12

AK16

LVDS or 2.5-V LVDS RX bit 12 or CMOS bit 57

127

HSMC_TX_D_N12

AH20

LVDS or 2.5-V LVDS TX bit 12n or CMOS bit 58

Table 2–21. HSMC Interface Pin Assignments, Schematic Signal Names, and Functions (Part 2 of 3)

Board

Reference (J7)

Schematic Signal Name

Cyclone V E

FPGA Pin

Number

I/O Standard

Description