Altera Stratix III Development Board User Manual

Page 13

Chapter 2: Board Components

2–5

Featured FPGA (U22)

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

shows the EP3SL150 I/O bank diagram from a system perspective.

f

For additional information about Altera devices, go to

.

QDRII+

1.5-V/1.8-V HSTL

66

Two CQ pins

Flash/P-SRAM/MAX

1.8-V CMOS

79

—

Ethernet

2.5-V CMOS

2.5-V LVDS

36

6, 2.5 V LVDS

User I/O (LEDs, etc)

1.8-V/2.5 V

30

—

14-pin LCD header

2.5-V CMOS

11

—

Graphics display

2.5-V CMOS

16

—

USB

2.5-V CMOS

0

—

HSMC Port A

2.5-V CMOS

2.5-V LVDS

88

3 clock inputs

HSMC Port B

2.5-V CMOS

2.5-V LVDS

88

3 clock inputs

Device I/O total: 628

Stratix III device I/O total: 736

Table 2–4. Stratix III Device Pin Count (Part 2 of 2)

Function

I/O Type

I/O Count

Special Pins

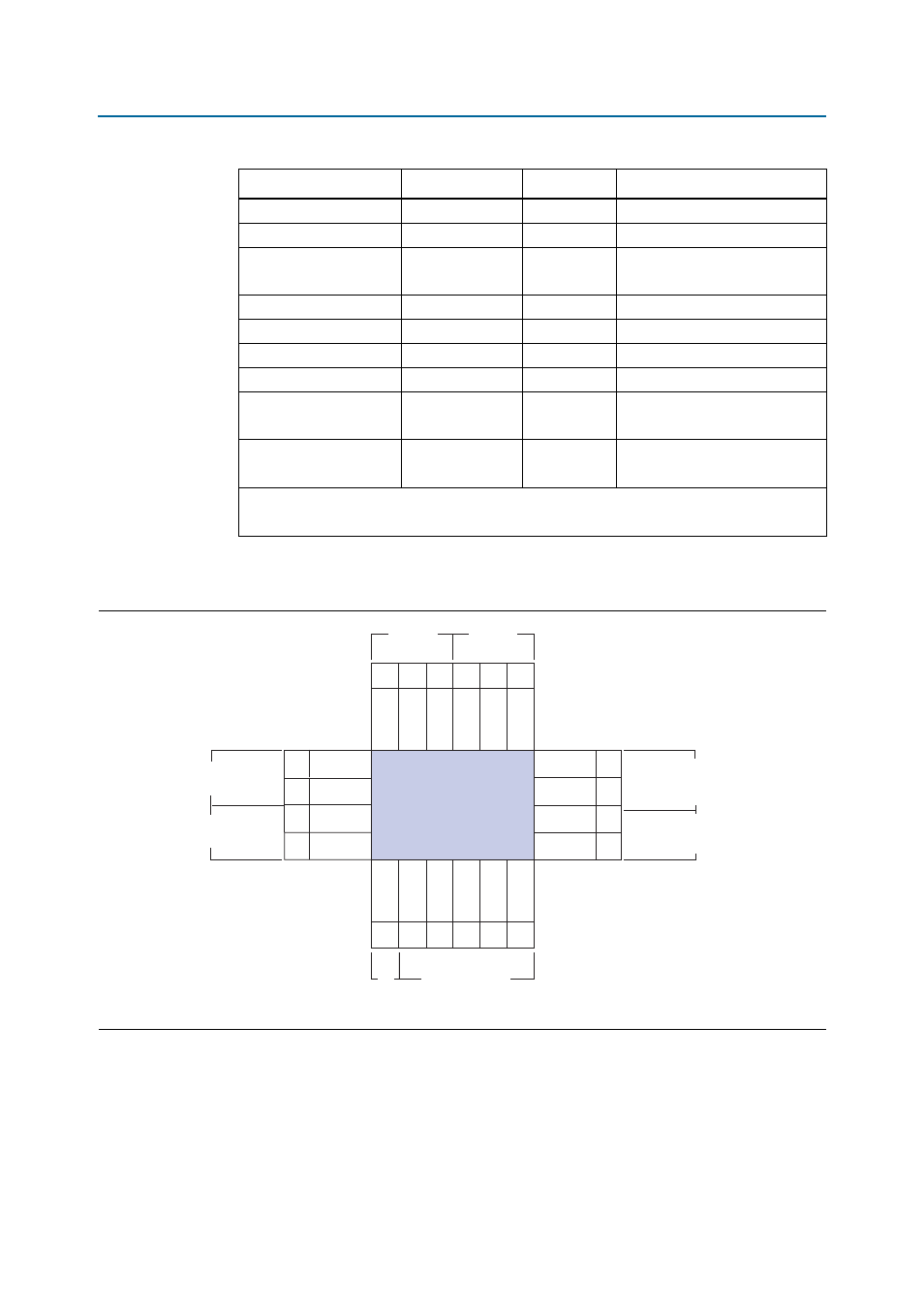

Figure 2–2. System I/O Bank Diagram

Bank 7A

40

Bank 7B

24

Bank 7C

32

Bank 8C

32

Bank 1A

48

Bank 1C

EP3SL150

QDR II

USER PB

1.5 V (73 pins)

2.5 V

(74 pins)

User, FLASH,

SRAM

1.8 V (98 pins)

40

Bank 2C

40

Bank 2A

Bank 6A

Bank 6C

Bank 5C

Bank 5A

48

48

40

40

48

Bank 8B

24

Bank 8A

40

Bank 4A

40

Bank 4B

24

Bank 4C

32

Bank 3C

32

Bank 3B

24

Bank 3A

40

LCD,

USER 7-SEG

2.5 V (35 pins)

DDR2 x 72 DIMM

1.8 V (136 pins)

HSMC A

2.5 V

(74 pins)

DDR2 x8

Devices

A & B

1.8 V

(70 pins)

2.5 V

(65 pins)

Ethernet,

Graphics LCD,

USB, Misc

HSMC B