High-speed mezzanine cards, High-speed mezzanine cards –41 – Altera Stratix III Development Board User Manual

Page 49

Chapter 2: Board Components

2–41

Components and Interfaces

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

lists the Ethernet PHY component reference and manufacturing

information.

High-Speed Mezzanine Cards

The board contains two HSMC interfaces called Port A and Port B. These HSMC

interfaces support both single-ended and differential signaling. The connector part

number is Samtec ASP-122953-01. The HSMC interface also allows for JTAG, SMBus,

clock outputs and inputs, as well as power for compatible HSMCs.

The HSMC is an Altera-developed specification, which allows users to expand the

functionality of the development board through the addition of daughter cards

(HSMCs).

U25 pin 90

GMII interface receive data bus bit 4

ENET_RX_D4

2.5 V

AH34

U25 pin 89

GMII interface receive data bus bit 5

ENET_RX_D5

2.5 V

AF29

U25 pin 87

GMII interface receive data bus bit 6

ENET_RX_D6

2.5 V

AH33

U25 pin 86

GMII interface receive data bus bit 7

ENET_RX_D7

2.5 V

V34

U25 pin 94

RGMII interface receive control

ENET_RX_DV

2.5 V

W5

U25 pin 3

GMII interface receive error

ENET_RX_ER

2.5 V

AJ10

U25 pin 75

SGMII interface receive data

ENET_RX_N

LVDS

Y34

U25 pin 77

SGMII interface receive data

ENET_RX_P

LVDS

AA33

U25 pin 80

SGMII interface (625 MHz) clock

ENET_S_CLKN

LVDS

W34

U25 pin 79

SGMII interface (625 MHz) clock

ENET_S_CLKP

LVDS

W33

U25 pin 4

MII interface (25 MHz) clock

ENET_TX_CLK

2.5 V

AB34

U25 pin 11

RGMII interface transmit data bus bit 0

ENET_TX_D[0]

2.5 V

AF28

U25 pin 12

RGMII interface transmit data bus bit 1

ENET_TX_D[1]

2.5 V

AD34

U25 pin 14

RGMII interface transmit data bus bit 2

ENET_TX_D[2]

2.5 V

AL34

U25 pin 16

RGMII interface transmit data bus bit 3

ENET_TX_D[3]

2.5 V

W30

U25 pin 17

RGMII interface transmit data bus bit 4

ENET_TX_D[4]

2.5 V

AD33

U25 pin 18

RGMII interface transmit data bus bit 5

ENET_TX_D[5]

2.5 V

AJ34

U25 pin 19

RGMII interface transmit data bus bit 6

ENET_TX_D[6]

2.5 V

AJ31

U25 pin 20

RGMII interface transmit data bus bit 7

ENET_TX_D[7]

2.5 V

AG30

U25 pin 9

RGMII interface transmit control

ENET_TX_EN

2.5 V

AA34

U25 pin 7

RGMII interface transmit error

ENET_TX_ER

2.5 V

AA29

U25 pin 81

SGMII interface transmit data

ENET_TX_N

LVDS

V29

U25 pin 82

SGMII interface transmit data

ENET_TX_P

LVDS

W28

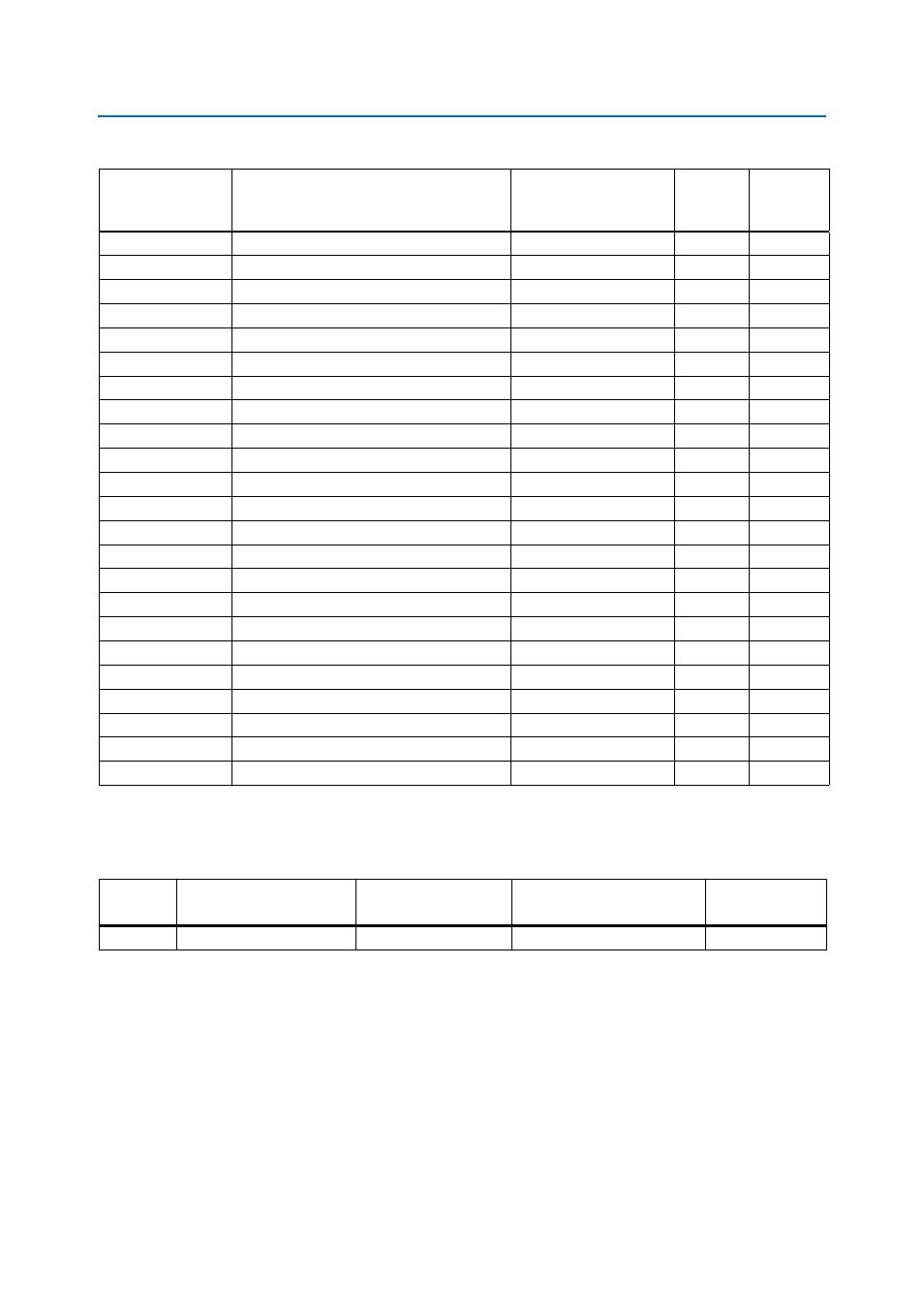

Table 2–39. Ethernet PHY (U25) Pin-Out (Part 2 of 2)

Board Reference

Description

Schematic Signal Name

I/O

Standard

Stratix III

Pin

Number

Table 2–40. Ethernet PHY Component Reference and Manufacturing Information

Board

Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U25

Ethernet PHY base-T device

Marvel Semiconductor

88E1111-B2-CAAIC000