Stratix iii fpga clock inputs, Stratix iii fpga clock inputs –26 – Altera Stratix III Development Board User Manual

Page 34

2–26

Chapter 2: Board Components

Clocking Circuitry

Stratix III 3SL150 Development Board

May 2013

Altera Corporation

Reference Manual

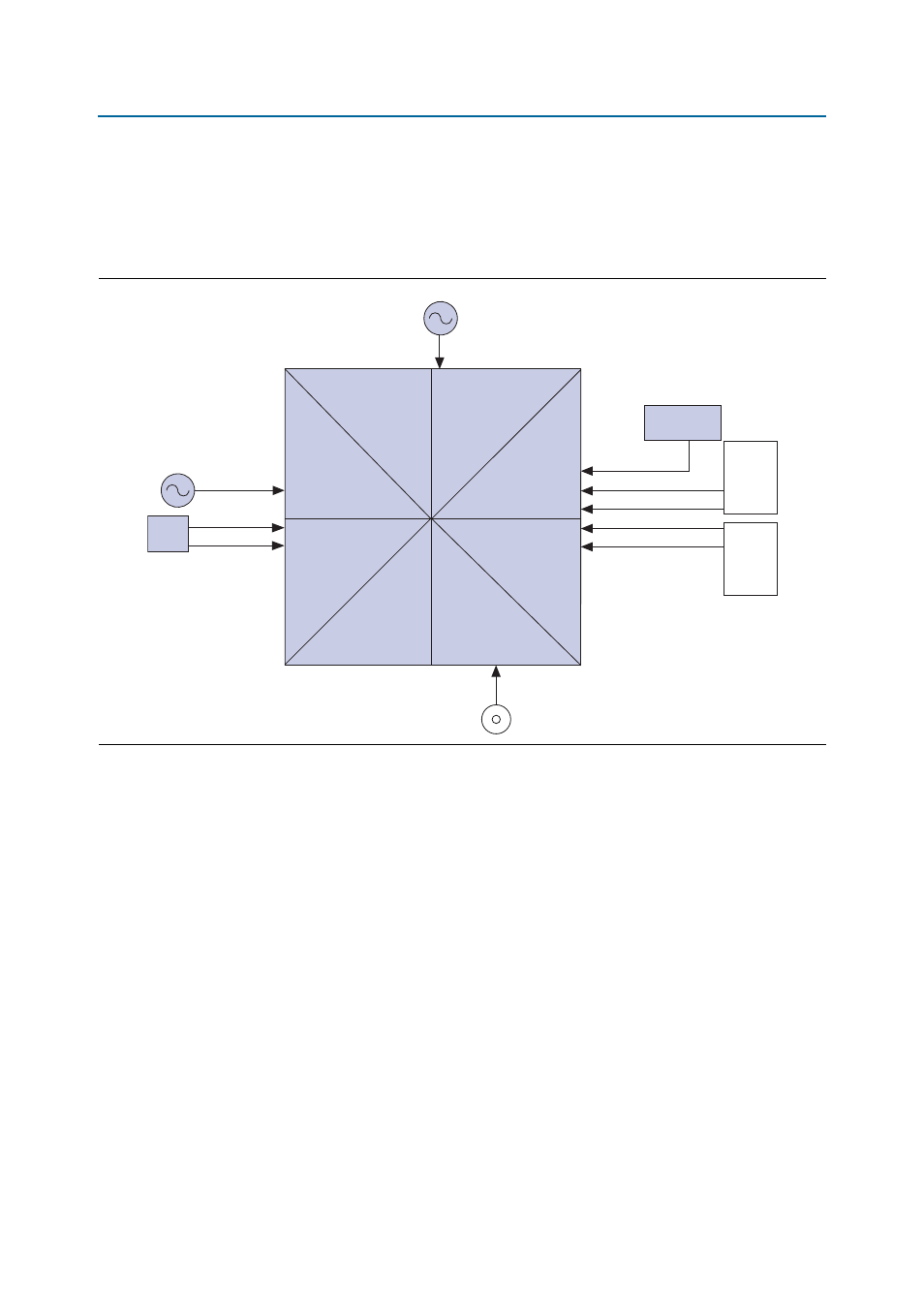

Stratix III FPGA Clock Inputs

outlines the inputs from the Stratix III FPGA. All PLL inputs are located in

the C sub-bank of each device bank. The clocks are sourced by the on-board

oscillators, SMA connectors, Ethernet, MAX II CPLD, and HSMC ports.

Figure 2–7. Stratix III FPGA Clock Inputs

Bank 8C

1.8 V

CLK14N

CLKIN_125

CLK14P

CLK15N

CLK15P

CLK12N

CLK12P

CLK13N

CLK13P

CLK5N

CLK5P

CLK4N

CLK4P

CLK7N

CLK7P

CLK6N

CLK6P

CLK1N

CLK1P

USB_IFCLK

500 MHz

CLK0N

CLK0P

CLK3N

CLK3P

CLK2N

CLK2P

ENET_S_CLKP

ENET_S_CLKN

CLK11N

CLK11P

CLK10N

CLK10P

CLK8N

CLK8P

CLK9N

CLK9P

Bank 7C

1.5 V

Bank 3C

1.8 V

Bank 4C

1.8 V

Bank 6C

2.5 V

Bank 5C

2.5 V

Bank 1C

1.8 V

Bank 2C

2.5 V

HSMA_CLK_IN_P2

HSMA_CLK_IN_N2

HSMB_CLK_IN_P2

HSMB_CLK_IN_N2

CLKIN_SMA

500 MHz

ENET

PHY

MAX II Device

HSMC

Port A

HSMC

Port B

SMA Input