Altera Stratix III Development Board User Manual

Page 21

Chapter 2: Board Components

2–13

MAX II CPLD

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

C12

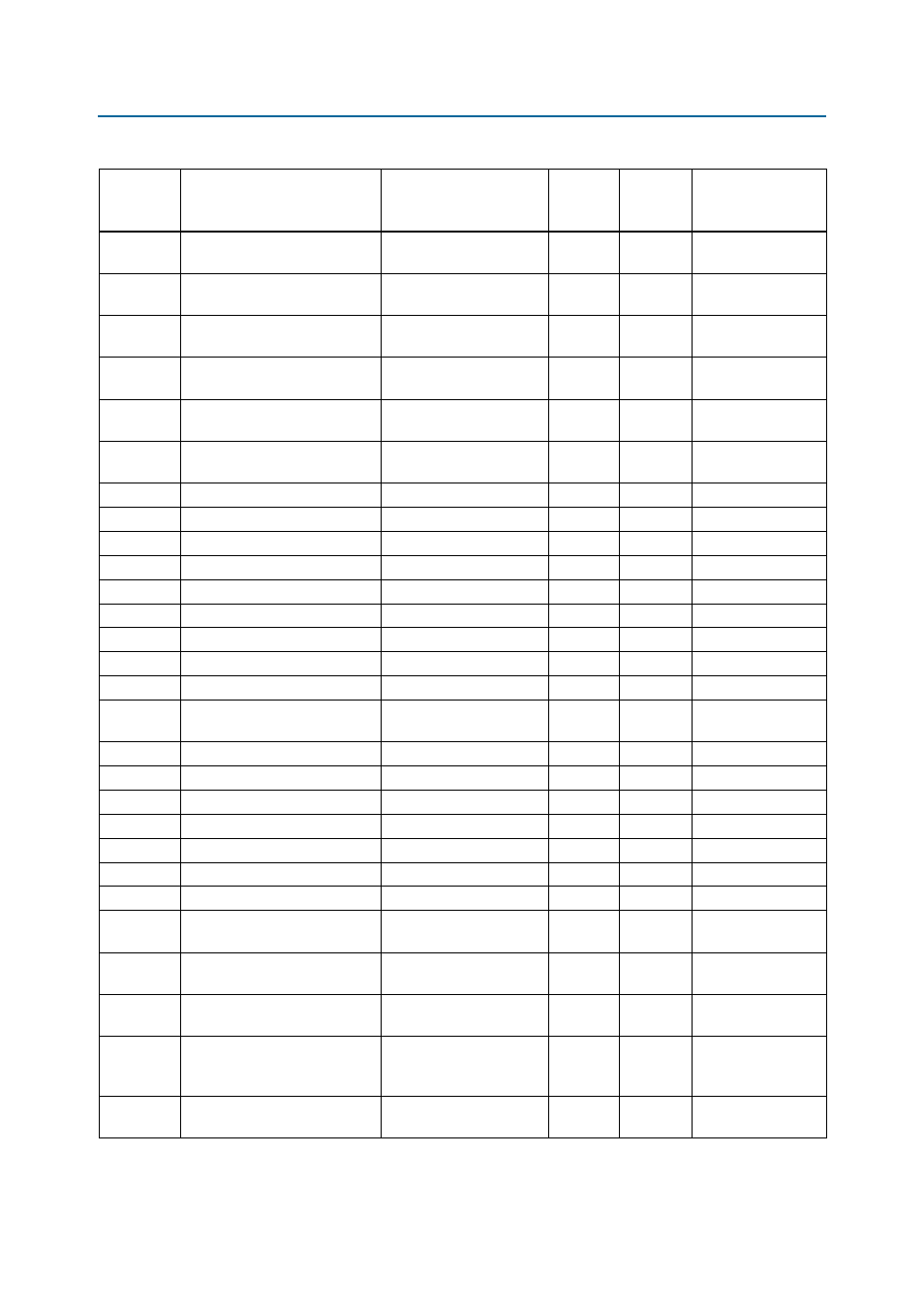

Cypress/FTDI USB data bus bit 2 USB_PHY_FD2

2.5 V

—

U12 pin 20 and U11

pin 23

A15

Cypress/FTDI USB data bus bit 3 USB_PHY_FD3

2.5 V

—

U12 pin 21 and U11

pin 22

D12

Cypress/FTDI USB data bus bit 4 USB_PHY_FD4

2.5 V

—

U12 pin 22 and U11

pin 21

B14

Cypress/FTDI USB data bus bit 5 USB_PHY_FD5

2.5 V

—

U12 pin 23 and U11

pin 20

C11

Cypress/FTDI USB data bus bit 6 USB_PHY_FD6

2.5 V

—

U12 pin 24 and U11

pin 19

B13

Cypress/FTDI USB data bus bit 7 USB_PHY_FD7

2.5 V

—

U12 pin 25 and U11

pin 18

D11

Cypress USB data bus bit 8

USB_PHY_FD8

2.5 V

—

U12 pin 45

A13

Cypress USB data bus bit 9

USB_PHY_FD9

2.5 V

—

U12 pin 46

E11

Cypress USB data bus bit 10

USB_PHY_FD10

2.5 V

—

U12 pin 47

B12

Cypress USB data bus bit 11

USB_PHY_FD11

2.5 V

—

U12 pin 48

C10

Cypress USB data bus bit 12

USB_PHY_FD12

2.5 V

—

U12 pin 49

A12

Cypress USB data bus bit 13

USB_PHY_FD13

2.5 V

—

U12 pin 50

D10

Cypress USB data bus bit 14

USB_PHY_FD14

2.5 V

—

U12 pin 51

B11

Cypress USB data bus bit 15

USB_PHY_FD15

2.5 V

—

U12 pin 52

C7

Cypress USB clock

USB_PHY_IFCLK

2.5 V

—

R89

A4

Cypress USB command/data

select

USB_PHY_CMD_DATA

2.5 V

—

U12 pin 29

E6

Cypress USB read enable

USB_PHY_REN

2.5 V

—

U12 pin 30

B4

Cypress USB write enable

USB_PHY_WEN

2.5 V

—

U12 pin 31

D6

Cypress USB empty

USB_PHY_EMPTY

2.5 V

—

U12 pin 1

C4

Cypress USB full

USB_PHY_FULL

2.5 V

—

U12 pin 29

C6

Cypress USB reset

USB_RESETn

2.5 V

—

U12 pin 41

B3

Cypress USB clock out

USB_CLKOUT

2.5 V

—

U12 pin 54

C5

Cypress USB wake up

USB_WAKEUP

2.5 V

—

U12 pin 44

B6

Cypress USB pin multiplexed for

I/O or FIFO select

USB_PA4_IF0ADR0

2.5 V

—

U12 pin 37

A2

Cypress USB pin multiplexed for

I/O or 8051 interrupt

USB_PA0_INT0n

2.5 V

—

U12 pin 33 and U11

pin 14

D5

Cypress USB pin multiplexed for

I/O or 8051 interrupt

USB_PA1_INT1n

2.5 V

—

U12 pin 34 and U11

pin 12

B1

Cypress USB pin multiplexed for

I/O or output enable for the

slave FIFOs.

USB_PA2_SLOE

2.5 V

—

U12 pin 35

D4

Cypress USB pin multiplexed for

I/O or alternate wake up signal

USB_PA3_WU2

2.5 V

—

U12 pin 36 and U11

pin 11

Table 2–5. MAX II Device Pin-out (Part 6 of 9)

MAX II

Pin Number

Description

Schematic Signal Name

I/O

Standard

Stratix III

Pin

Number

Other Connections