Chapter 6 systemverilog tutorials, Verifying a slave dut – Altera Mentor Verification IP Altera Edition AMBA AXI4-Stream User Manual

Page 67

Mentor Verification IP AE AMBA AXI4-Stream User Guide, V10.3

67

April 2014

Chapter 6

SystemVerilog Tutorials

This chapter discusses how to use the Mentor VIP AE master and slave BFMs to verify slave

and master DUT components, respectively.

tutorial, the slave is verified using a master BFM and test

program. In the

tutorial, the master issues “transfers” that are verified

using a slave BFM and test program.

Following this top-level discussion of how you verify a master and a slave component using the

Mentor VIP AE is a brief example of how to run Qsys, the powerful system integration tool in

Quartus

®

II software. This procedure shows you how to use Qsys to create a top-level DUT

environment. For more details about this example, refer to “

Getting Started with Qsys and the

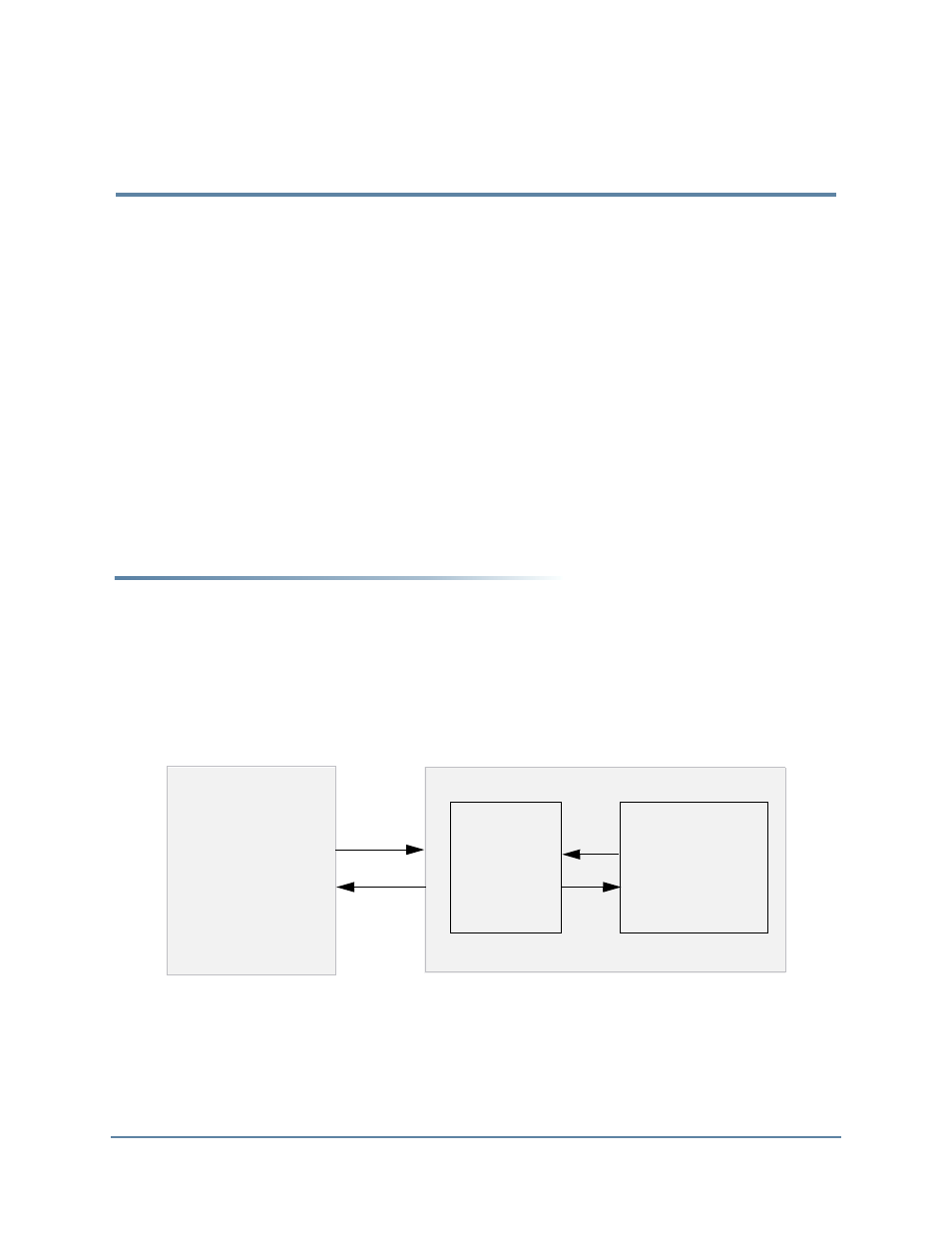

Verifying a Slave DUT

A slave DUT component is connected to a master BFM at the signal level. A master test

program written at the transaction level generates stimulus using the master BFM to verify the

slave DUT.

illustrates a typical top-level test bench environment.

Figure 6-1. Slave DUT Top-Level Test Bench Environment

A top-level file instantiates and connects all the components required to test and monitor the

DUT, and controls the system clock (ACLK) and reset (ARESETn) signals.

Master

BFM

On-chip

RAM slave

Master

Test

program

Top-level file