Verifying a master dut, Slave bfm test program, Basic slave test program api definition – Altera Mentor Verification IP Altera Edition AMBA AXI4-Stream User Manual

Page 71

SystemVerilog Tutorials

Verifying a Master DUT

Mentor Verification IP AE AMBA AXI4-Stream User Guide, V10.3

71

April 2014

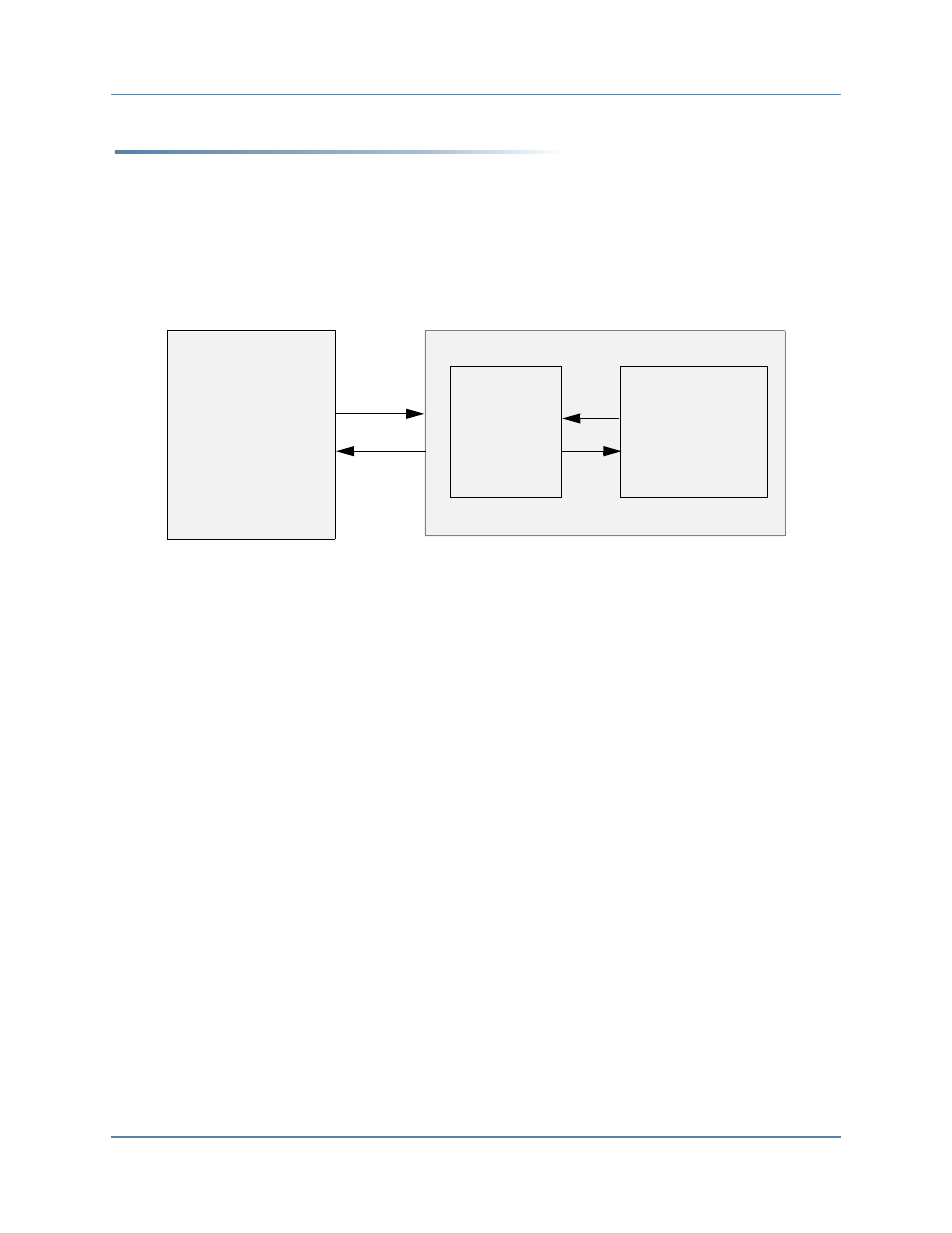

Verifying a Master DUT

A master DUT component is connected to a slave BFM at the signal level. A slave test program

written at the transaction level generates stimulus using the slave BFM to verify the master

DUT.

illustrates a typical top-level test bench environment.

Figure 6-2. Master DUT Top-Level Test Bench Environment

A top-level file instantiates and connects all the components required to test and monitor the

DUT, and controls the system clock (ACLK) and reset (ARESETn) signals.

Slave BFM Test Program

The slave test program contains a

Basic Slave Test Program API Definition

simplified interface for you to start verifying a master DUT with minimal effort. The API

allows the slave BFM to control back-pressure to the master DUT by configuring the delay for

the assertion of the TREADY signal. No other slave test program editing is required in this case.

Advanced Slave Test Program API Definition

allows the slave BFM to receive protocol

transfers and insert a delay for the assertion of the TREADY signal. No further analysis of the

protocol transfer content is performed. If further analysis is required then the slave test program

will require editing to add this feature.

For a complete code listing of the slave test program, refer to “

Basic Slave Test Program API Definition

The Basic Slave Test Program API contains the following:

•

Configuration variable

to insert a delay in the assertion of the TREADY

protocol signal.

Slave

BFM

Master

DUT

Slave

test

program

Top-level file