Program configuration push button, Program select push button, General user input/output – Altera Arria V SoC Development Board User Manual

Page 27: User-defined push buttons, General user input/output –19, User-defined push buttons –19

Chapter 2: Board Components

2–19

General User Input/Output

July 2014

Altera Corporation

Reference Manual

Program Configuration Push Button

The program configuration push button, PGM_CONFIG (S12), is an input to the MAX V

CPLD 5M2210 System Controller. This input forces a FPGA reconfiguration from the

flash memory. The location in the flash memory is based on the settings of

PGM_LED[2:0]

, which is controlled by the program select push button, PGM_SEL (S13).

Valid settings include PGM_LED0, PGM_LED1, or PGM_LED2 on the three pages in flash

memory reserved for FPGA designs.

Program Select Push Button

The program select push button, PGM_SEL (S13), is an input to the MAX V CPLD

System Controller. This push button toggles the PGM_LED[2:0]sequence that selects

which location in the flash memory is used to configure the FPGA. Refer to

for the PGM_LED[2:0] sequence definitions.

General User Input/Output

This section describes the user I/O interface to the FPGA, including the push buttons,

DIP switches, LEDs, expansion header, and character LCD.

User-Defined Push Buttons

The development board includes eight user-defined push buttons. For information

about the system and safe reset push buttons, refer to

Board references S1–S8 are push buttons for controlling the FPGA designs that loads

into the Arria V SoC device. Push buttons S1–S4 connect to the FPGA while push

buttons S5–S8 connect to the HPS. When you press and hold down the switch, the

device pin is set to logic 0; when you release the switch, the device pin is set to logic 1.

There are no board-specific functions for these general user push buttons.

lists the user-defined push button schematic signal names and their

corresponding Arria V SoC pin numbers.

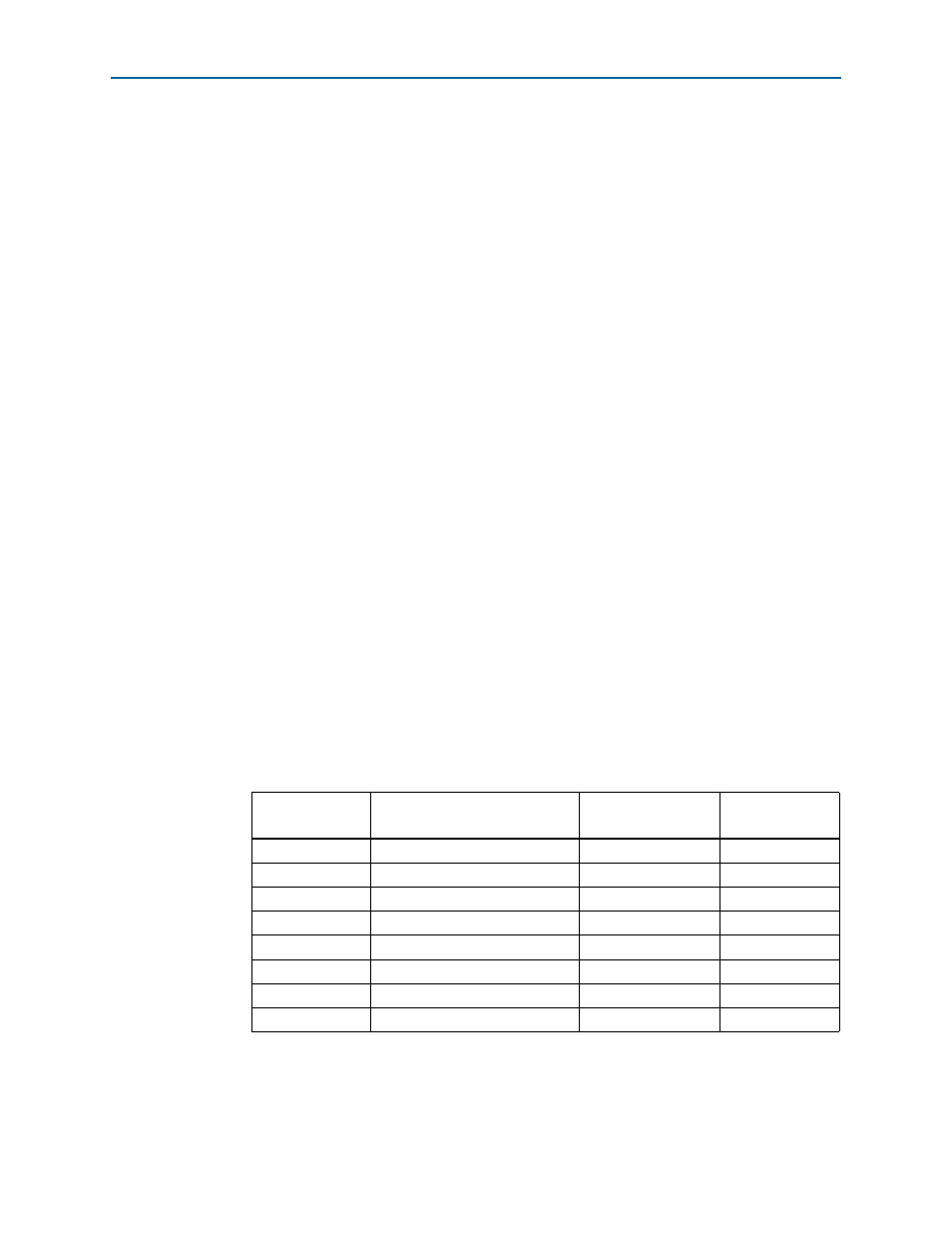

Table 2–11. User-Defined Push Button Schematic Signal Names and Functions

Board Reference

Schematic Signal Name

Arria V SoC Pin

Number

I/O Standard

S4

USER_PB_FPGA0

AT23

1.5-V

S3

USER_PB_FPGA1

AP24

1.5-V

S2

USER_PB_FPGA2

AW24

1.5-V

S1

USER_PB_FPGA3

AW23

1.5-V

S8

USER_PB_HPS0

E15

2.5-V

S7

USER_PB_HPS1

G16

2.5-V

S6

USER_PB_HPS2

E16

2.5-V

S5

USER_PB_HPS3

H16

2.5-V