Fmc –29 – Altera Arria V SoC Development Board User Manual

Page 37

Chapter 2: Board Components

2–29

Components and Interfaces

July 2014

Altera Corporation

Reference Manual

FMC

The development board contains two high pin count (HPC) FPGA mezzanine card

(FMC) ports that functions with a quadrature amplitude modulation (QAM) digital-

to-analog converter (DAC) FMC module or daughter card. This pinout satisfies a

QAM DAC that requires 58 LVDS data output pairs, one LVDS input clock pair, and

three low-voltage differential signaling (LVDS) control pairs from the Arria V. These

pins also have the option to be used as single-ended I/O pins. The VCCIO supply for

FMC bank A in the low pin count (LPC) and HPC provide a variable voltage of 1.5 V,

1.8 V, 2.5 V (default), or 3.3 V. The VCCIO supply for FMC bank B in the HPC

provides a variable voltage from 1.2 V to 3.3 V, which can be supplied by the FMC

module. For device safety concerns, a jumper is available for you to connect this bank

to the same VCCIO used for FMC bank A. This allows the VCCIO pins on the FPGA

to be tied to a known power. The VCCIO pins also allows you the option to perform a

manual check for the module’s input voltage before connecting to the FPGA. This is to

ensure that the module does not exceed the power supply maximum voltage rating.

lists the FMC port A pin assignments, signal names, and functions.

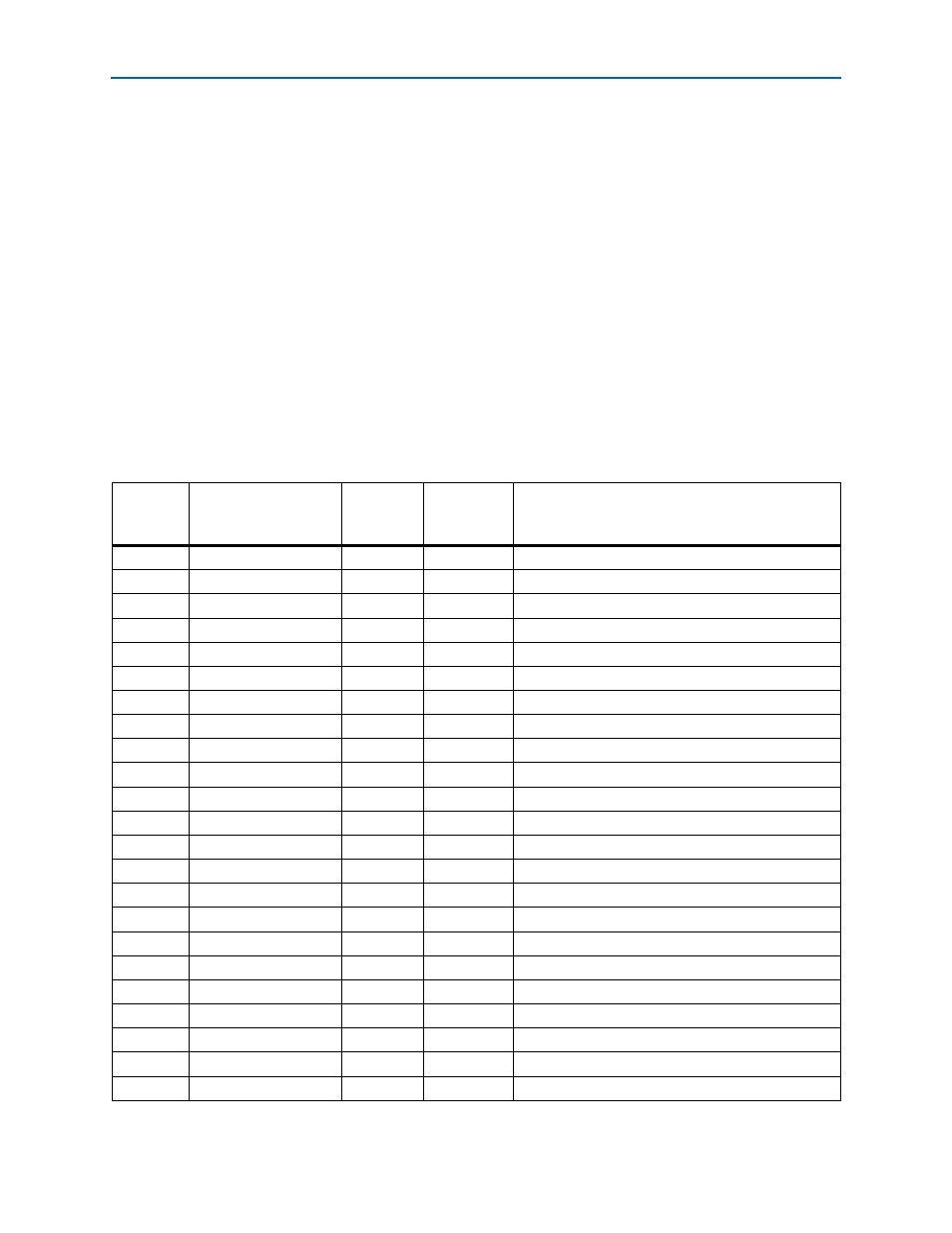

Table 2–21. FMC Port A Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 5)

Board

Reference

(J26)

Schematic

Signal Name

Arria V SoC

Pin Number

I/O Standard

Description

D1

FMC_C2M_PG

—

2.5-V CMOS

Power good output

H4

FMC_CLK_M2C_P0

B22

LVDS

Clock input 0

H5

FMC_CLK_M2C_N0

C22

LVDS

Clock input 0

G2

FMC_CLK_M2C_P1

A22

LVDS

Clock input 1

G3

FMC_CLK_M2C_N1

A21

LVDS

Clock input 1

C3

FMC_DP_C2M_N0

AE36

PCML

Transmit channel

A23

FMC_DP_C2M_N1

AA36

PCML

Transmit channel

A27

FMC_DP_C2M_N2

W36

PCML

Transmit channel

A31

FMC_DP_C2M_N3

R36

PCML

Transmit channel

A35

FMC_DP_C2M_N4

N36

PCML

Transmit channel

A39

FMC_DP_C2M_N5

J36

PCML

Transmit channel

B37

FMC_DP_C2M_N6

G36

PCML

Transmit channel

B33

FMC_DP_C2M_N7

C36

PCML

Transmit channel

C2

FMC_DP_C2M_P0

AE37

PCML

Transmit channel

A22

FMC_DP_C2M_P1

AA37

PCML

Transmit channel

A26

FMC_DP_C2M_P2

W37

PCML

Transmit channel

A30

FMC_DP_C2M_P3

R37

PCML

Transmit channel

A34

FMC_DP_C2M_P4

N37

PCML

Transmit channel

A38

FMC_DP_C2M_P5

J37

PCML

Transmit channel

B36

FMC_DP_C2M_P6

G37

PCML

Transmit channel

B32

FMC_DP_C2M_P7

C37

PCML

Transmit channel

C7

FMC_DP_M2C_N0

AF38

PCML

Receive channel

A3

FMC_DP_M2C_N1

AB38

PCML

Receive channel