Files generated for altera ip cores, Files generated for altera ip cores -8 – Altera Hybrid Memory Cube Controller User Manual

Page 17

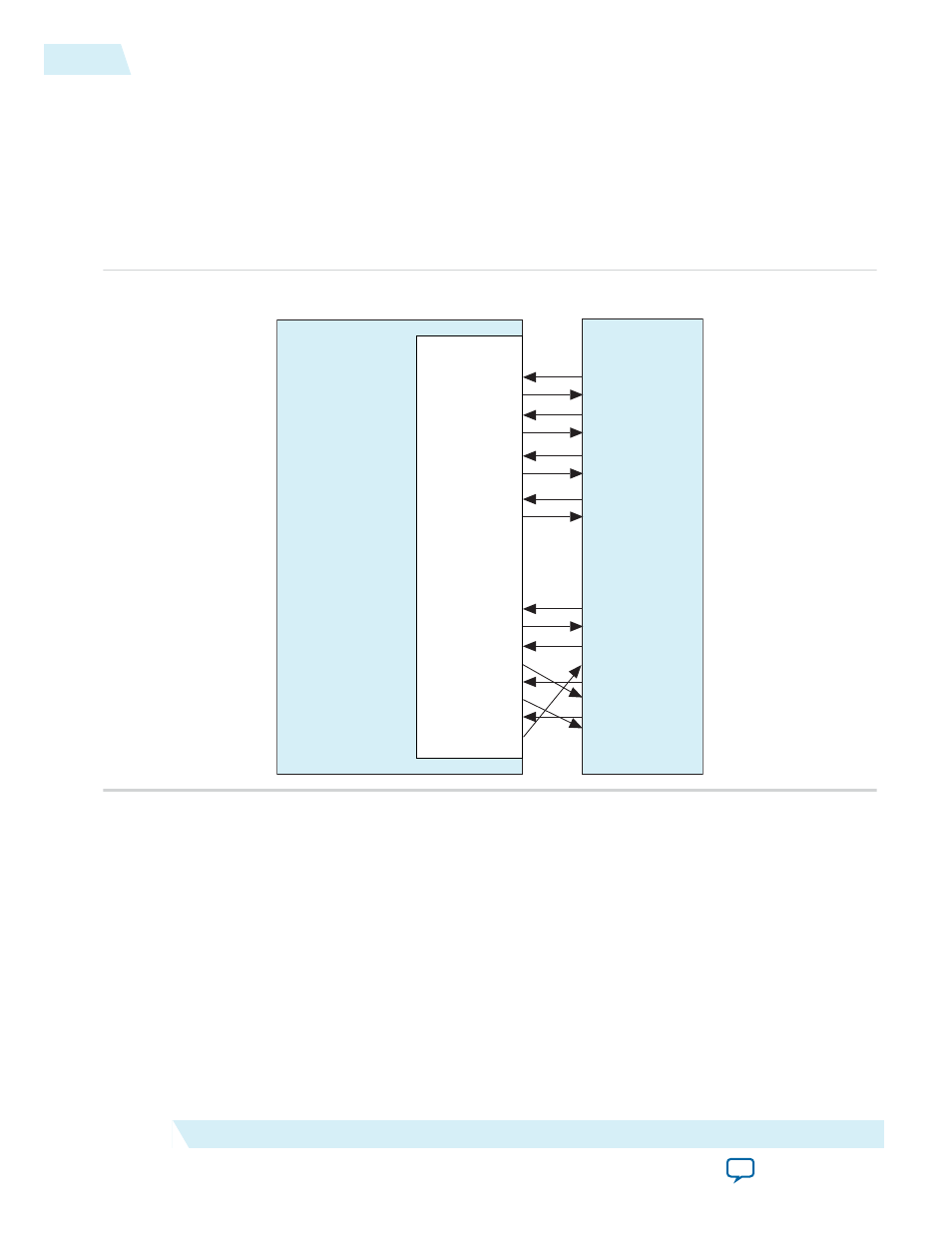

Figure 2-4: Non-Default TX Mapping Parameter Value Example

If you connect the HMC Controller IP core

hmc_lxtx[2:0]

output signals according to the table, and

connect all other IP core

hmc_lxtx[<i>]

output ports to the corresponding HMC device

LxRX[<i>]

input ports, you would set the value of the TX mapping parameter to 0xFEDCBA9876543021 to

compensate for the non-standard connection.

Note: The TX mapping parameter specifies the HMC device lane by position and the IP core lane by

value. The figure illustrates a mapping parameter value of 0xFED.......43021 and not a value of

0xFED....43102.

FPGA

HMC Controller

Hybrid Memory Cube

hmc_lxtx[0]

LxRX[0]

LxTX[0]

hmc_lxrx[0]

hmc_lxtx[1]

LxRX[1]

LxTX[1]

hmc_lxrx[1]

hmc_lxtx[2]

LxRX[2]

LxTX[2]

hmc_lxrx[2]

hmc_lxtx[3]

LxRX[3]

LxTX[3]

hmc_lxrx[3]

hmc_lxtx[F]

LxRX[F]

LxTX[F]

hmc_lxrx[F]

hmc_lxtx[E]

LxRX[E]

LxTX[E]

hmc_lxrx[E]

hmc_lxtx[D]

LxRX[D]

LxTX[D]

hmc_lxrx[D]

hmc_lxtx[C]

LxRX[C]

LxTX[C]

hmc_lxrx[C]

. . .

. . .

. . .

RX mapping value 0xFEDCBA9876543210

TX mapping value 0xFEDCBA9876543021

Use caution in modifying these parameters. In loopback configurations, you must ensure the RX

mapping and TX mapping parameters specify reversed mappings. Otherwise, the IP core downstream of

the RX lane swapper appears to receive data on the wrong lanes.

Files Generated for Altera IP Cores

The Quartus II software generates multiple files during generation of your IP core variation.

2-8

Files Generated for Altera IP Cores

UG-01152

2015.05.04

Altera Corporation

Getting Started with the HMC Controller IP Core