Flow control, Error detection and management, Flow control -7 – Altera Hybrid Memory Cube Controller User Manual

Page 35: Error detection and management -7

This feature enhances data reliability but increases request-to-response latency and resource utilization.

Enabling this feature might reduce the maximum operating frequency (f

MAX

) and might increase the

difficulty of closing timing in full-width variations.

Related Information

Error and Retry Statistics Registers

Describes the

RETRY_ECC_COUNT

and

RESPONSE_ECC_COUNT

registers.

Information about the built-in ECC feature in Arria 10 devices.

Flow Control

The HMC specification describes two possible flow control schemes for host-to-HMC traffic, token based

flow control and Response Open Loop Mode.

In token-passing mode, the device sends information about its buffering capacity to the HMC link partner

during transaction layer initialization. In Response Open Loop Mode, the device does not send informa‐

tion about its buffering capacity to the HMC link partner. Instead, it only sends a request packet when it

has room to receive the response at any time.

The HMC Controller IP core operates in Response Open Loop Mode. The IP core is designed to have the

capacity to accept all response packets from the HMC device.

When user requests come in faster than the HMC Controller IP core can send them out on the HMC link,

the HMC Controller IP core backpressures the application by deasserting the

dp_req_ready

signal.

Error Detection and Management

The HMC specification defines error detection and recovery processes. The HMC Controller IP core

complies with these requirements, and implements the following additional features to support error

management:

• Error Response queues to support software handling without dropping Error Responses that arrive in

quick succession

• Statistics registers that count the number of packets in various error categories

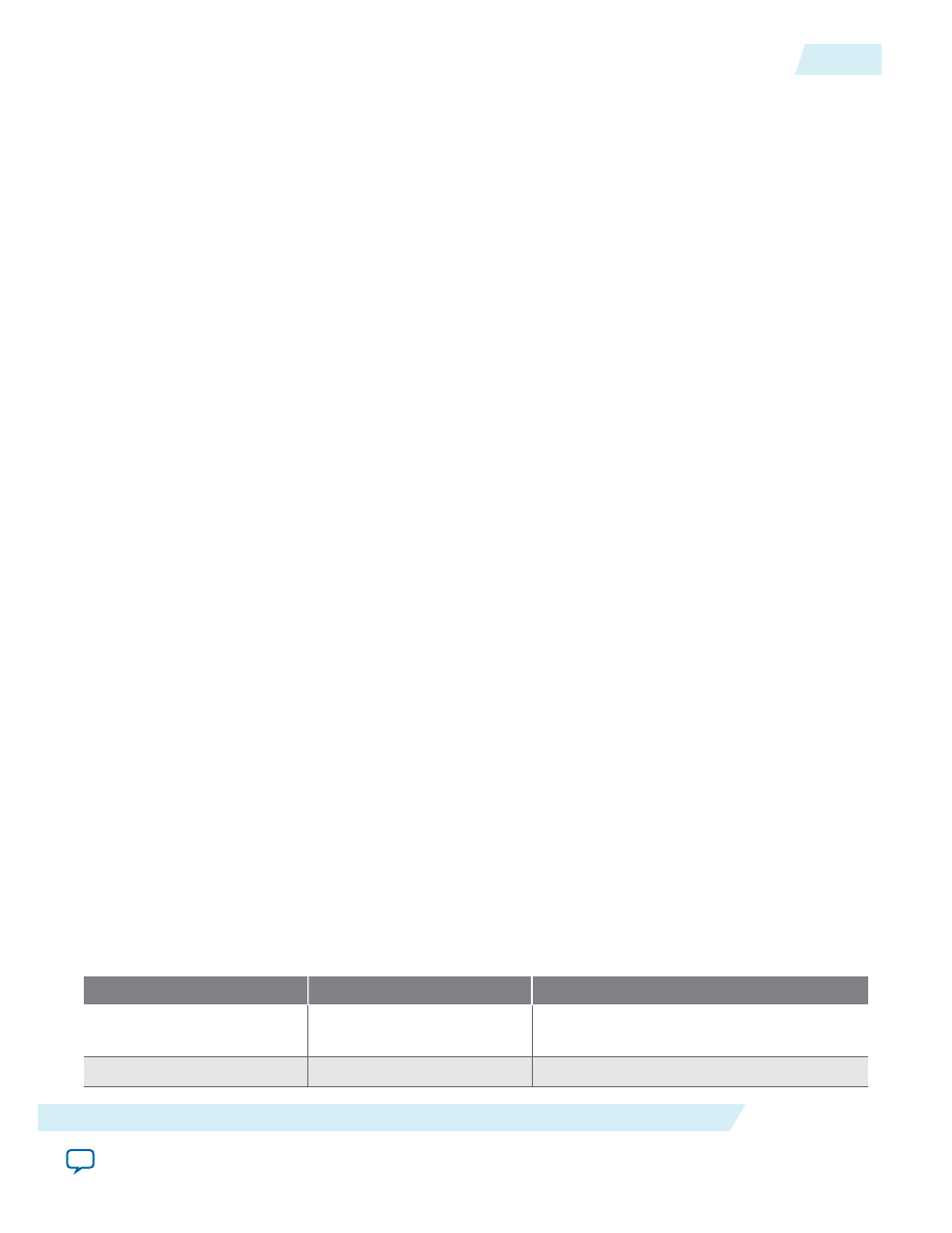

Table 3-2: HMC Response Packet Field Checking

The HMC Controller checks these HMC response packet fields for error indications, and handles errors by

entering Error Abort mode to force the HMC device to retransmit the packet. In this mode, the IP core completes

transmission of any partially transmitted packet and then submits IRTRY packets, per the HMC specification. The

IP core also sets the indicated bit in the

INTERRUPT_STATUS

register and increments the

Local Count

field of the

LOCAL_ERROR_COUNT

register.

Response Packet Field

Error Indication

INTERRUPT_STATUS Register Bit

LNG

and

DLN

The two fields have different

values, or an invalid value

LNG/DLN Error

CRC

Incorrect CRC

CRC Error

UG-01152

2015.05.04

Flow Control

3-7

Functional Description

Altera Corporation