Altera Hybrid Memory Cube Controller User Manual

Page 42

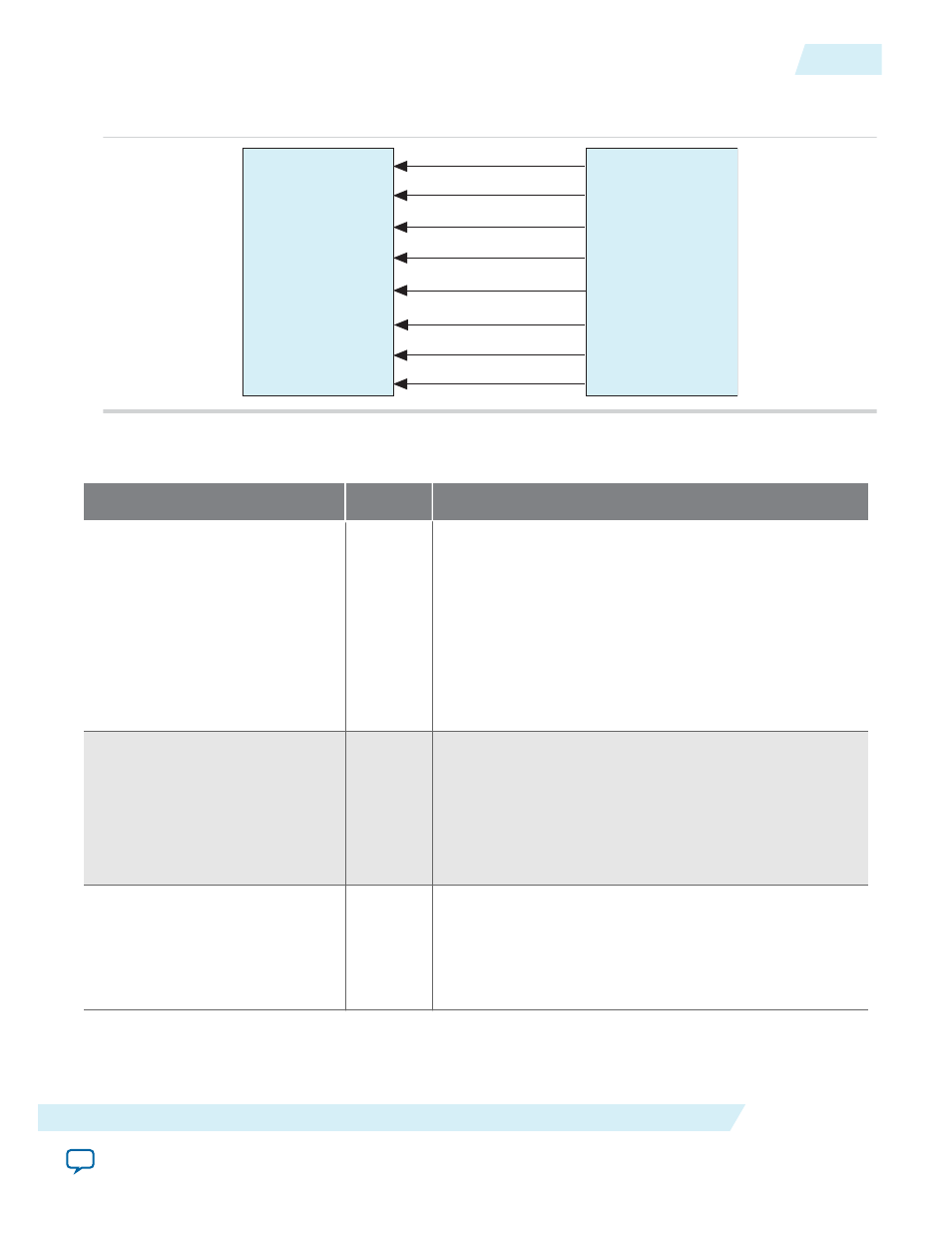

Figure 4-2: HMC Controller IP Core to RX Application

The HMC Controller IP core acts as a source and the client acts as a sink in the receive direction.

dp_rsp_valid

dp_rsp_tag[8:0]

dp_rsp_cmd[5:0]

dp_rsp_size[2:0]

dp_rsp_data[255:0] or [511:0]

dp_rsp_error

dp_rsp_sop

dp_rsp_eop

HMC Controller

IP Core

RX Client

Logic

Table 4-2: Signals of the Data Path Response Interface

All interface signals are clocked by the

core_clk

clock.

Signal Name

Direction

Description

dp_rsp_valid

Output

Indicates that all of the

dp_rsp_tag

,

dp_rsp_cmd

,

dp_

rsp_error

,

dp_rsp_sop

, and

dp_rsp_eop

signals are

valid, and in a read response with payload,

dp_rsp_data

and

dp_rsp_size

are valid.

The application must accept all valid transactions. You

cannot back-pressure the HMC Controller IP core data

path response interface.

The IP core maintains this signal asserted for the duration

of a multi-cycle read data transfer.

dp_rsp_tag[8:0]

Output

The tag associated with the original request to which this

is a response.

After you process this response, the tag is available for re-

use.

The IP core maintains the value of this signal for the

duration of a multi-cycle read data transfer.

dp_rsp_cmd[5:0]

Output

Indicates the packet command associated with this

response. Refer to Table 25 in the HMC Specification v1.1

for the command encodings.

The IP core maintains the value of this signal for the

duration of a multi-cycle read data transfer.

UG-01152

2015.05.04

Application Response Interface

4-5

HMC Controller IP Core Signals

Altera Corporation