Adding the external pll, Fpga – Altera Hybrid Memory Cube Controller User Manual

Page 20

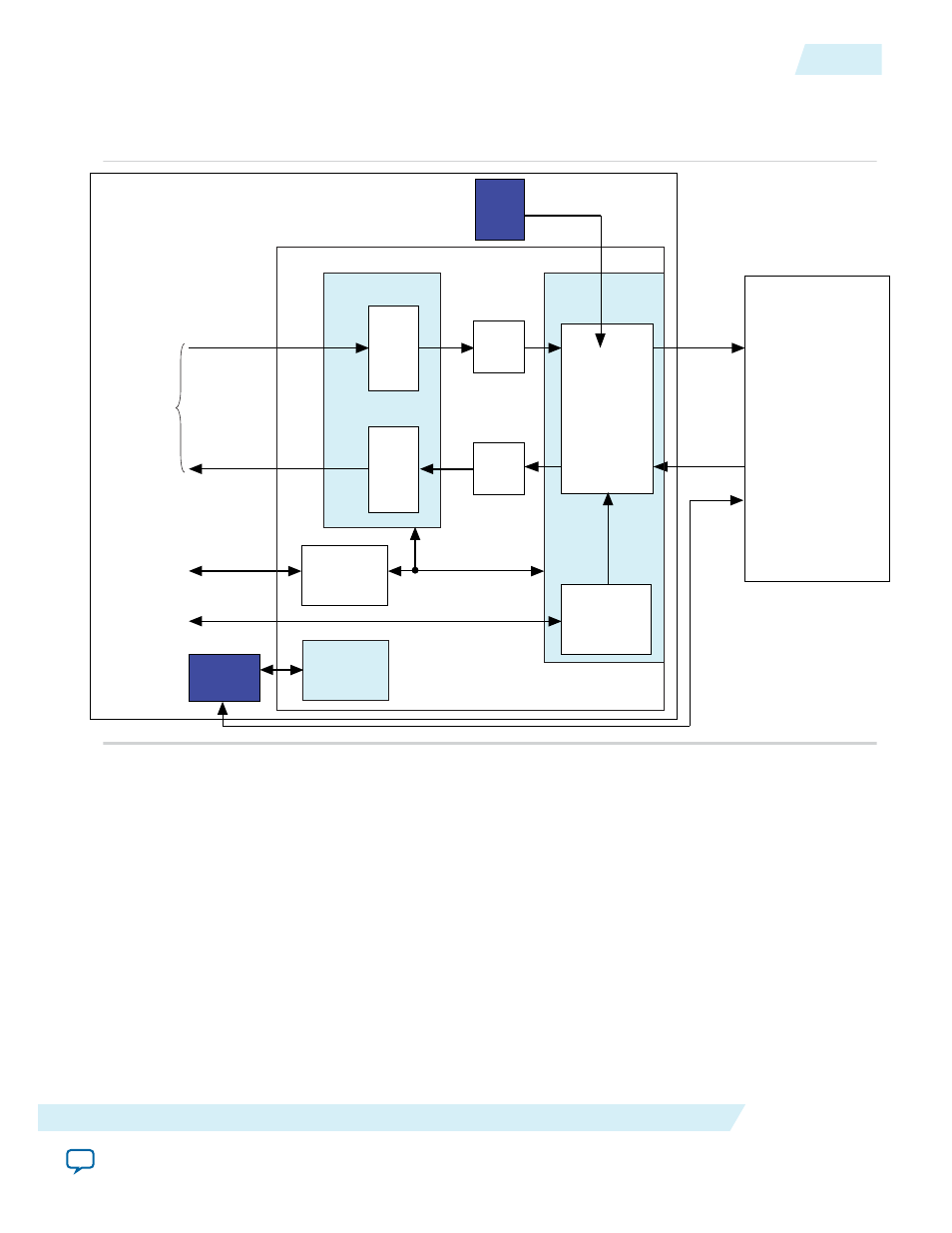

Figure 2-6: Required External Blocks

The required external blocks appear darker than the other blocks in the figure. The external TX PLL IP

core configures an ATX PLL in the device transceiver or an fPLL in Transceiver mode.

HMC Controller IP Core

FPGA

TX

FIFO

TX

RX

Control and

Status Interface

Initialization

Initialization

State Machine

State Machine

Arria 10

Transceiver

Reconfiguration

Interface

Avalon-MM

Application

Interface

TX Lane

Swapper

RX Lane

Swapper

Avalon-MM

I C Master

Transceiver

x8

or

x16

TX PLLs

HMC Device

2

Adding the External PLL

The HMC Controller IP core requires that you generate and connect external transceiver PLL IP cores.

You must generate the number of PLL IP cores required to clock the transceiver channels that are

configured as HMC Controller IP core lanes. Each ATX PLL IP core configures the transceiver PLL in the

transceiver in hardware, but you must generate the transceiver PLL IP core separately from the HMC

Controller IP core in software. You can also configure an fPLL in transceiver mode. If you do not generate

and connect the transceiver PLL IP core or cores, the HMC Controller IP core does not function correctly

in hardware.

You can use the IP Catalog to generate each external PLL IP core that configures a transceiver PLL on the

device. In the IP Catalog, select Arria 10 Transceiver ATX PLL or Arria 10 fPLL.

UG-01152

2015.05.04

Adding the External PLL

2-11

Getting Started with the HMC Controller IP Core

Altera Corporation