Control register, Control register -2 – Altera Hybrid Memory Cube Controller User Manual

Page 54

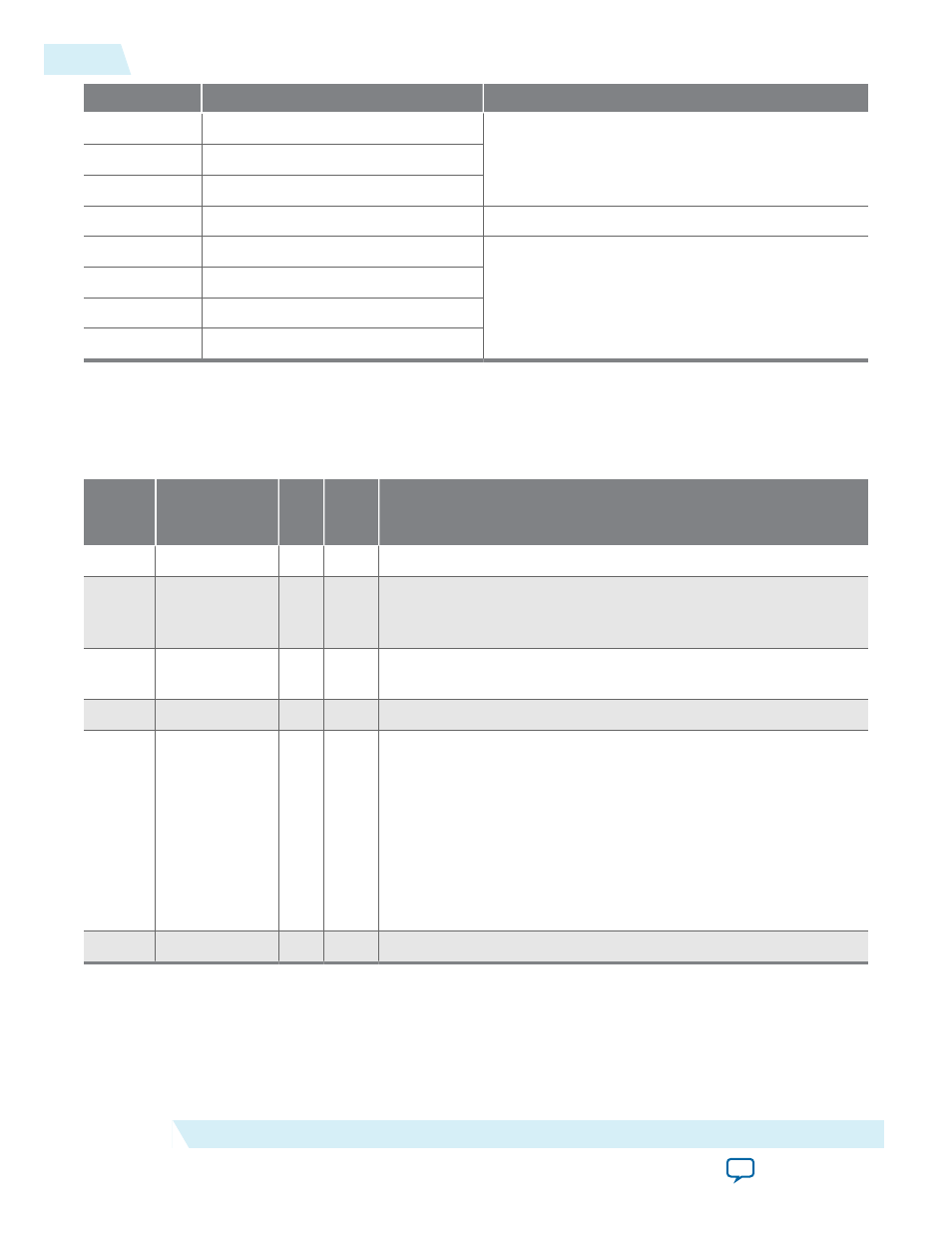

Offset

Register Name

Location of Additional Information

0x20

INTERRUPT_STATUS

0x24

INTERRUPT_ENABLE

0x28

GLOBAL_INTERRUPT_ENABLE

0x2C

Reserved

0x30

LOCAL_ERROR_COUNT

Error and Retry Statistics Registers

0x34

REMOTE_ERROR_COUNT

0x38

RETRY_BUFFER_ECC_COUNT

0x3C

RESPONSE_BUFFER_ECC_COUNT

CONTROL Register

Table 5-3: HMC Controller IP Core CONTROL Register at Offset 0x04

Bits

Field Name

Type Value

on

Reset

Description

31:10 Reserved

RO 0

9

ForceRXError

WO 0x0

Writing the value of 1 to this register field forces the HMC

Controller IP core to detect an error in the input stream and send

a StartRetry request to the HMC device. This bit is self-clearing.

8

CRCErrorInjec

t

WO 0x0

Writing the value of 1 to this register field injects a single bit error

in the CRC of the next request packet. This bit is self-clearing.

7:2

Reserved

RO 0x00

1

ClearFatalErr

or

WO 0x0

If the Retry State Machine (RSM) is in fatal error state (RetryFata‐

lError), writing the value of 1 to this register field causes the RSM

to resume normal operation.

When a RetryFatalError occurs, the RSM halts and waits for

external corrective action. Writing the value of 1 to this register

field forces the RSM to continue.

This bit is self-clearing. It clears whether or not it affects the RSM

state.

0

Reserved

RO 0x00

Related Information

on page 3-8

5-2

CONTROL Register

UG-01152

2015.05.04

Altera Corporation

HMC Controller IP Core Register Map