Control and status interface signals, Control and status interface signals -10 – Altera Hybrid Memory Cube Controller User Manual

Page 47

Related Information

HMC Controller IP Core Example Design

The HMC Controller example design includes an I

2

C master module that correctly implements the four-

way handshaking protocol with the HMC Controller IP core, and that implements the recommended

sequence of register writes to initialize the Micron HMC 15G SR HMC device.

Control and Status Interface Signals

The control and status register interface is an Avalon-MM interface that provides access to the HMC

Controller IP core internal control and status registers. This interface does not provide access to the

transceiver configuration registers.

The Avalon-MM interface implements a standard memory-mapped protocol. You can connect any

Avalon master—for example, an embedded processor or JTAG Avalon master—to this bus to access the

IP core control and status registers.

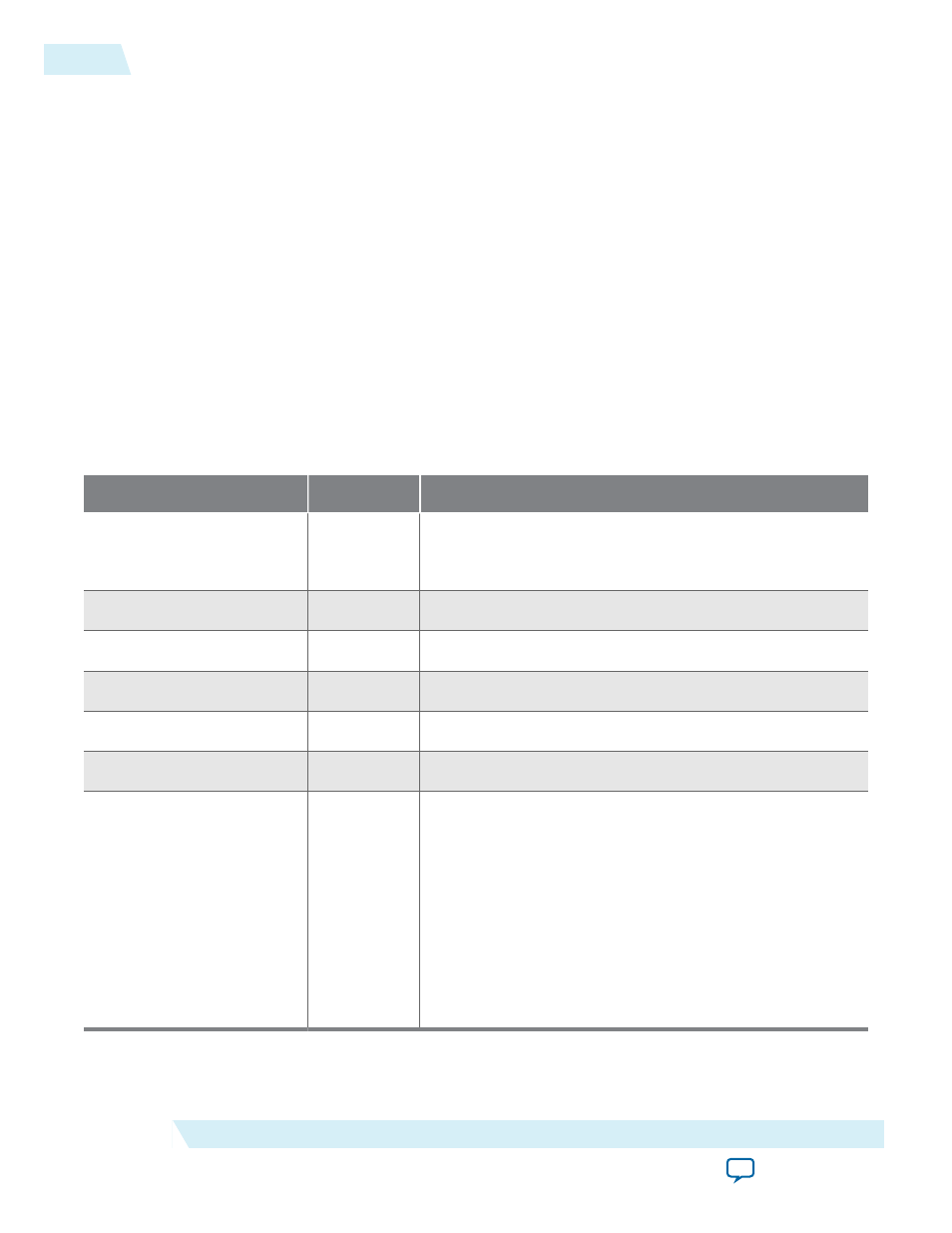

Table 4-5: Control and Status Interface Signals

The

core_clk

clocks the signals on the HMC Controller IP core control and status interface. This interface

supports only read operations and write operations with a 32-bit payload (one full register value).

Signal Name

Direction

Description

csr_address[5:0]

Input

Byte address for register reads and writes. All HMC

Controller control and status registers are 32 bits wide.

Therefore, all addresses are 4-byte aligned.

csr_read

Input

You must assert this signal to request a read transfer

csr_write

Input

You must assert this signal to request a write transfer

csr_writedata[31:0]

Input

Write data

csr_readdata[31:0]

Output

Read data

csr_readdatavalid

Output

Read data is ready for use

csr_irq

Output

Interrupt request.

The value of this signal is not associated with the current

values of other signals on this interface. The IP core asserts

this interrupt signal asynchronously as soon as an

INTERRUPT_STATUS

register bit is asserted (if the relevant

INTERRUPT_ENABLE

bit is set and the

GLOBAL_INTERRUPT_

ENABLE

register's

GlobalEnable

bit has the value of 1) and

maintains the signal asserted until either one of the two

relevant enable bits is reset, or the application writes the

value of 1 to all currently-asserted

INTERRUPT_STATUS

register bits.

4-10

Control and Status Interface Signals

UG-01152

2015.05.04

Altera Corporation

HMC Controller IP Core Signals