Altera Hybrid Memory Cube Controller User Manual

Page 40

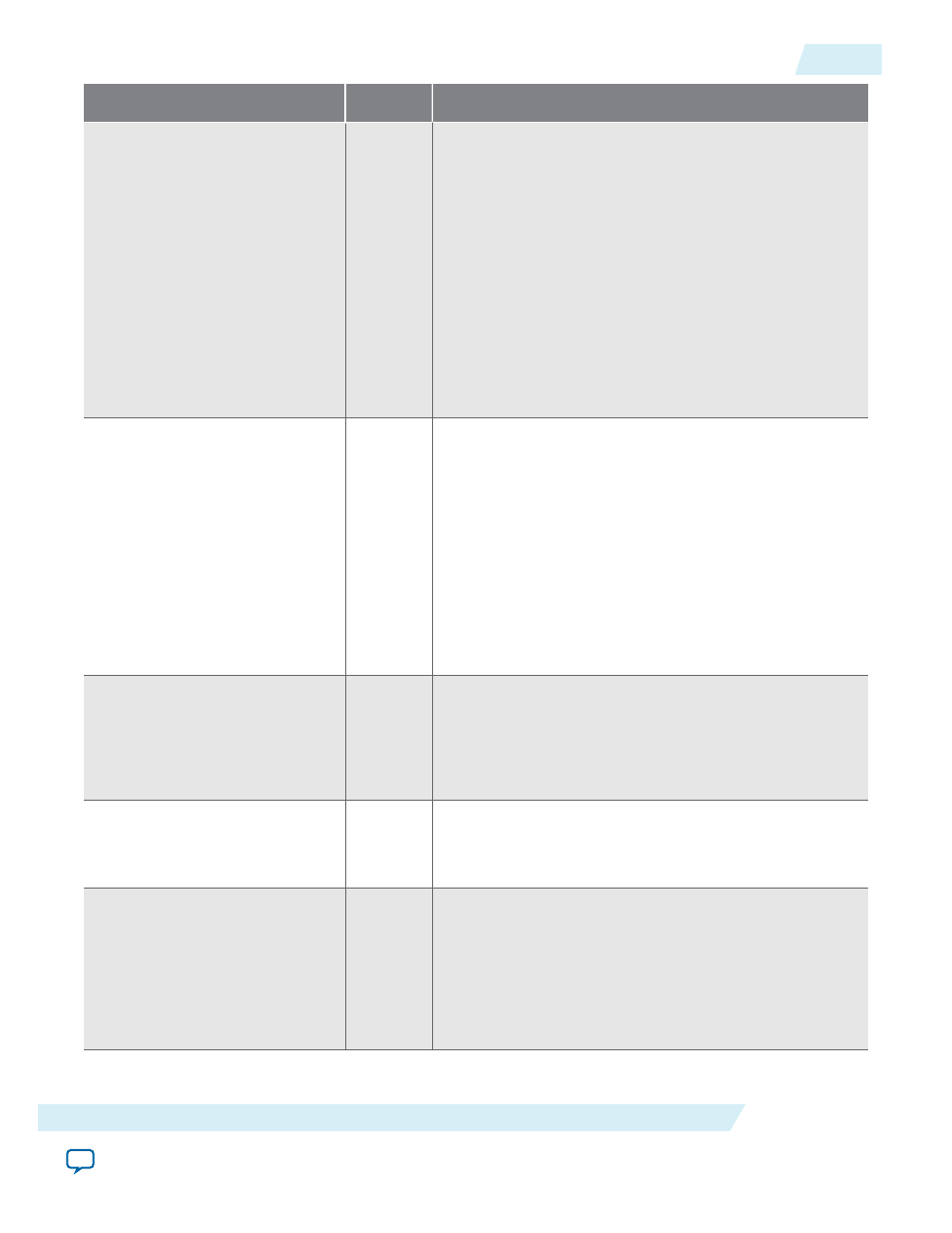

Signal Name

Direction

Description

dp_req_valid

Input

Indicates that the transaction is valid—all input signals

have valid values. The HMC Controller IP core accepts

data on the rising edge of

core_clk

when both

dp_req_

ready

and

dp_req_valid

are asserted.

The application must maintain this signal asserted during

a multi-cycle write data transfer.

The application can send back-to-back requests by

maintaining the

dp_req_valid

signal asserted.

Note: The application must update the value it drives

on

dp_req_tag

for the new request. If the

application continues to drive the old values on

the input signals, that new request has the same

tag as the previous request.

dp_req_tag[8:0]

Input

The user-generated tag associated with this request. The

corresponding response returns with the identical tag.

The value of this signal is a Don't Care for posted transac‐

tion requests. Because these requests have no

corresponding response that must be identified, they do

not require meaningful tag values.

You must ensure every tag in use at any given time by a

non-posted transaction is unique. After a response

returns, the tag is available for re-use.

The application must maintain the value on this signal

during a multi-cycle write data transfer.

dp_req_cmd[5:0]

Input

Indicates the packet command associated with this

request. Refer to Table 17 in the HMC Specification v1.1

for the command encodings.

The application must maintain the value on this signal

during a multi-cycle write data transfer.

dp_req_cube[2:0]

Input

The CUB ID of the cube to which the request is directed.

The application must maintain the value on this signal

during a multi-cycle write data transfer.

dp_req_addr[33:0]

Input

Target address in the external HMC device. Current HMC

devices ignore the four least significant bits of the address

(and assumes they have the value of 4'b0000) in all

requests the HMC Controller IP core generates, except for

the BIT WRITE request.

The application must maintain the value on this signal

during a multi-cycle write data transfer.

UG-01152

2015.05.04

Application Request Interface

4-3

HMC Controller IP Core Signals

Altera Corporation