Error_response register, Interrupt related registers, Error_response register -5 – Altera Hybrid Memory Cube Controller User Manual

Page 57: Interrupt related registers -5

ERROR_RESPONSE Register

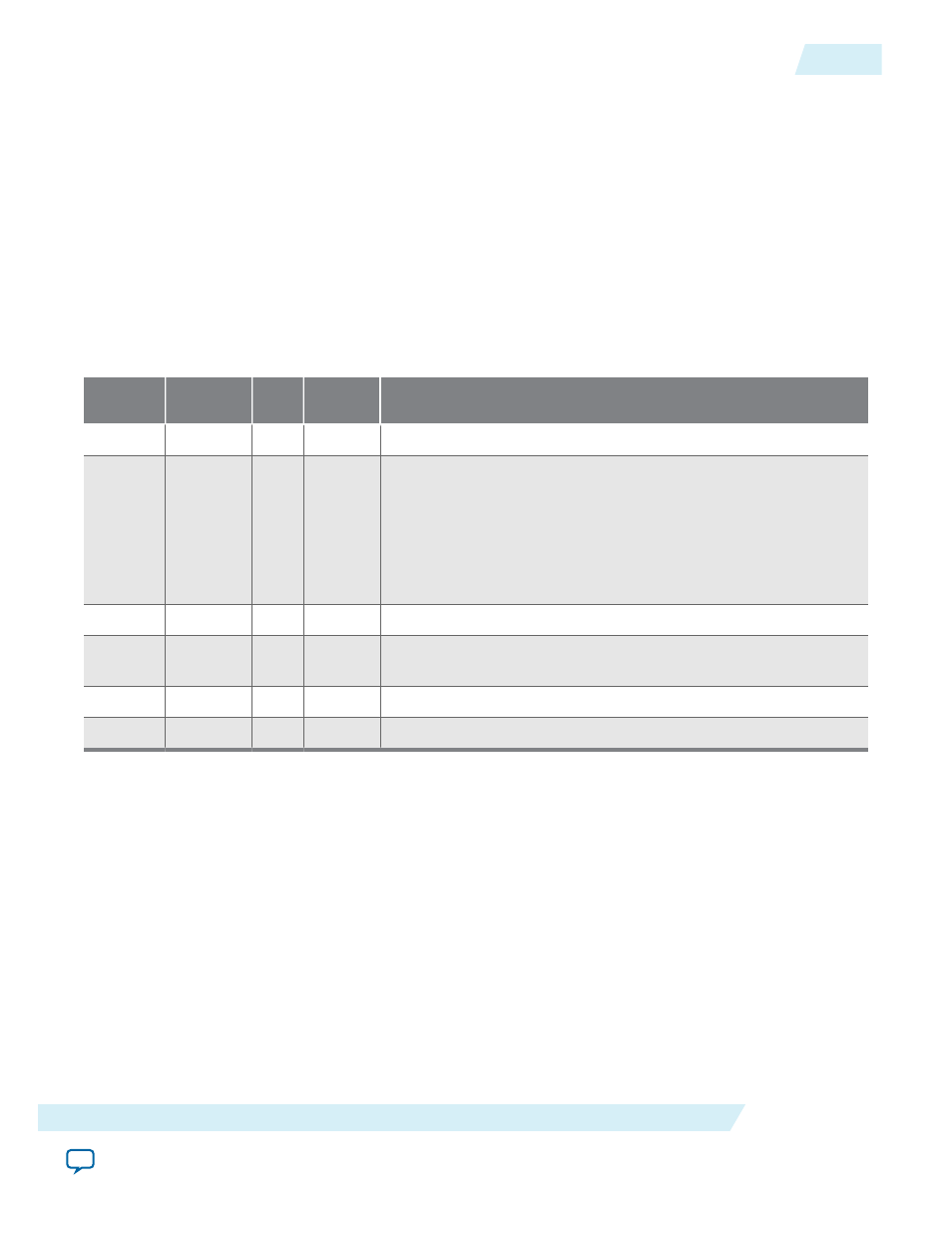

Table 5-7: HMC Controller IP Core ERROR_RESPONSE Register at Offset 0x14

The HMC Controller IP core stores the

ERRSTAT

and

CUB

fields of the Error responses that it receives on the HMC

link. The IP core stores these fields in an internal Error Response queue (FIFO buffer). The application can read

the relevant information for each Error Response packet from this queue by reading the

ERROR_RESPONSE

register.

Reading from the register advances the queue.

Read, Write, or MODE response packets the HMC Controller IP core receives with a non-zero

ERRSTAT

field do

not route to this queue or register. Instead they are sent to the data path response interface with

dp_rsp_error

asserted.

Bits

Field Name Type Value on

Reset

Description

31:17 Reserved

RO

0x0000

16

Valid

RO

0x0

Indicates the

CUB

and

ERRSTAT

fields in the register hold valid

values. When the Error Response queue is empty, the

CUB

and

ERRSTAT

fields are not valid, and the

Valid

bit has the value of 0.

You can poll the

Valid

bit to determine if any Error Response

packets are waiting to be processed, or you can enable the

RX

Error Response

interrupt in the

INTERRUPT_ENABLE

register.

15:11 Reserved

RO

0x00

10:8

CUB

RO

0x0

The CUB ID extracted from the

TAG

field of the Error Response

packet.

7

Reserved

RO

0x0

6:0

ERRSTAT

RO

0x00

The

ERRSTAT

value extracted from the Error Response packet.

Related Information

Information about the encoding of the

ERRSTAT

response packet field is available in Table 16 in the HMC

specification.

Interrupt Related Registers

THE HMC Controller IP core has three interrupt-related registers.

•

INTERRUPT_STATUS

: Register bits report individual interrupt source status.

•

INTERRUPT_ENABLE

: Register bits individually enable the corresponding interrupts in the

INTERRUPT_STATUS

register to trigger assertion of the IP core

csr_irq

output signal, unless the

GLOBAL_INTERRUPT_ENABLE

register turns off this ability.

•

GLOBAL_INTERRUPT_ENABLE

: Register allows you to disable all interrupt responses or to enable those

interrupt sources indicated in the

INTERRUPT_ENABLE

register.

UG-01152

2015.05.04

ERROR_RESPONSE Register

5-5

HMC Controller IP Core Register Map

Altera Corporation