Error and retry statistics registers, Error and retry statistics registers -9 – Altera Hybrid Memory Cube Controller User Manual

Page 61

Bits

Field Name

Type

Value on

Reset

Description

0

GlobalEnable

RW 0x0

Writing the value of 0 to this register field disables all

interrupt sources from asserting the

csr_irq

output signal.

Writing the value of 1 to this register field allows the IP core

to assert the

csr_irq

output signal according to the

interrupt sources enabled in the

INTERRUPT_ENABLE

register

at offset 0x24. An interrupt source causes the IP core to

assert the

csr_irq

output signal only if the

GlobalEnable

register field and the relevant

INTERRUPT_ENABLE

register

field both have the value of 1.

Error and Retry Statistics Registers

The HMC Controller IP core has four statistics registers. Counter fields in these registers are all of type

RC (Read to Clear).

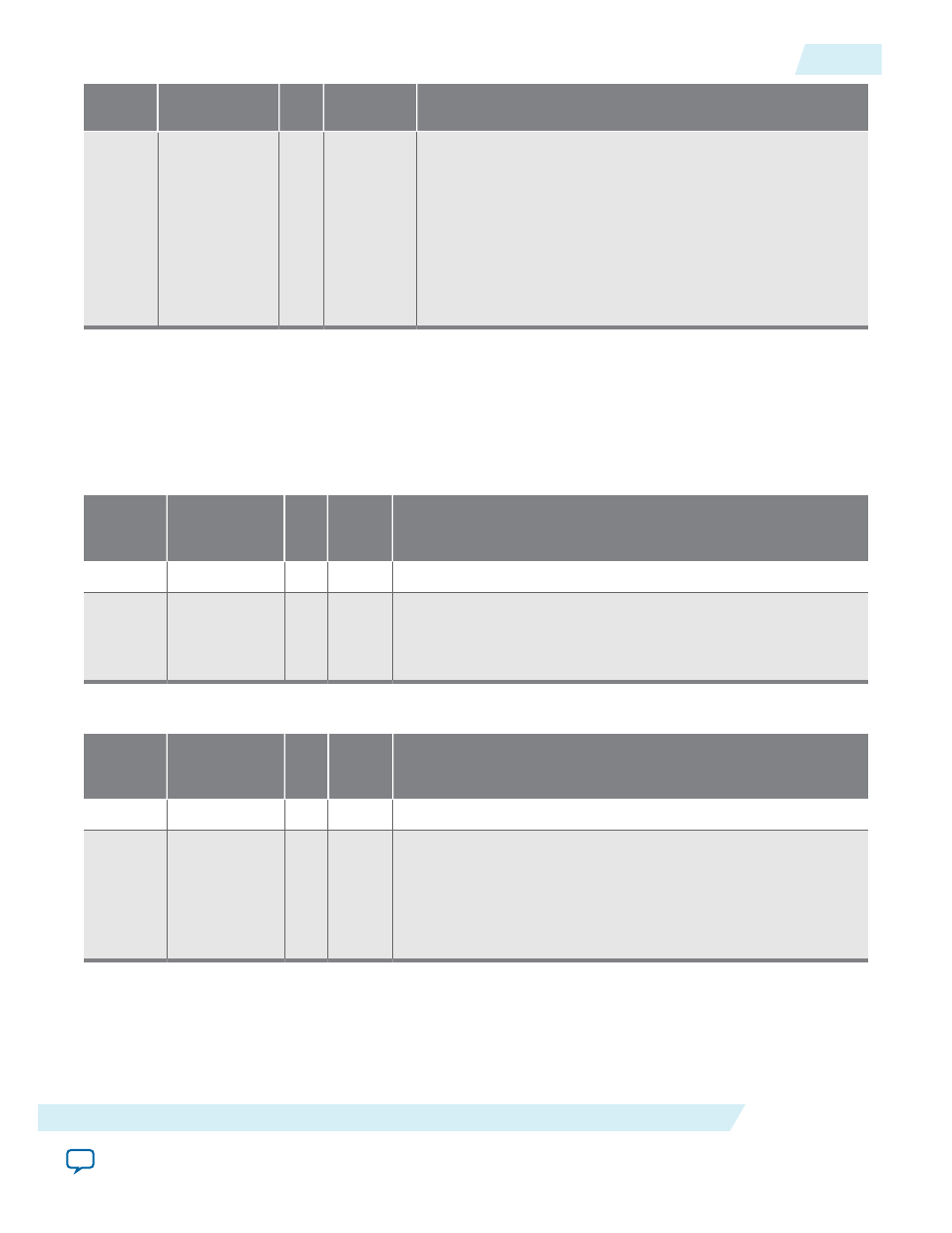

Table 5-11: HMC Controller IP Core LOCAL_ERROR_COUNT Register at Offset 0x30

Bits

Field Name

Typ

e

Value

on

Reset

Description

31:16

Reserved

RO 0x0000

15:0

Local Count

RC 0x0000 Count of received packets with CRC, SEQ, or length errors. The

counter saturates at 0xFFFF.

Reading this register clears the

Local Count

field.

Table 5-12: HMC Controller IP Core REMOTE_ERROR_COUNT Register at Offset 0x34

Bits

Field Name

Typ

e

Value

on

Reset

Description

31:16

Reserved

RO 0x0000

15:0

Error Count

RC 0x0000 Number of times the HMC Controller IP core began the output

error recovery process and retransmitted packets. This number

indicates the number of errors detected by the external HMC

device. This counter saturates at 0xFFFF.

Reading this register clears the

Error Count

field.

UG-01152

2015.05.04

Error and Retry Statistics Registers

5-9

HMC Controller IP Core Register Map

Altera Corporation