Integrating your ip core in your design, Pin constraints, Integrating your ip core in your design -9 – Altera Hybrid Memory Cube Controller User Manual

Page 18: Pin constraints -9, Figure 2-5: ip core generated files

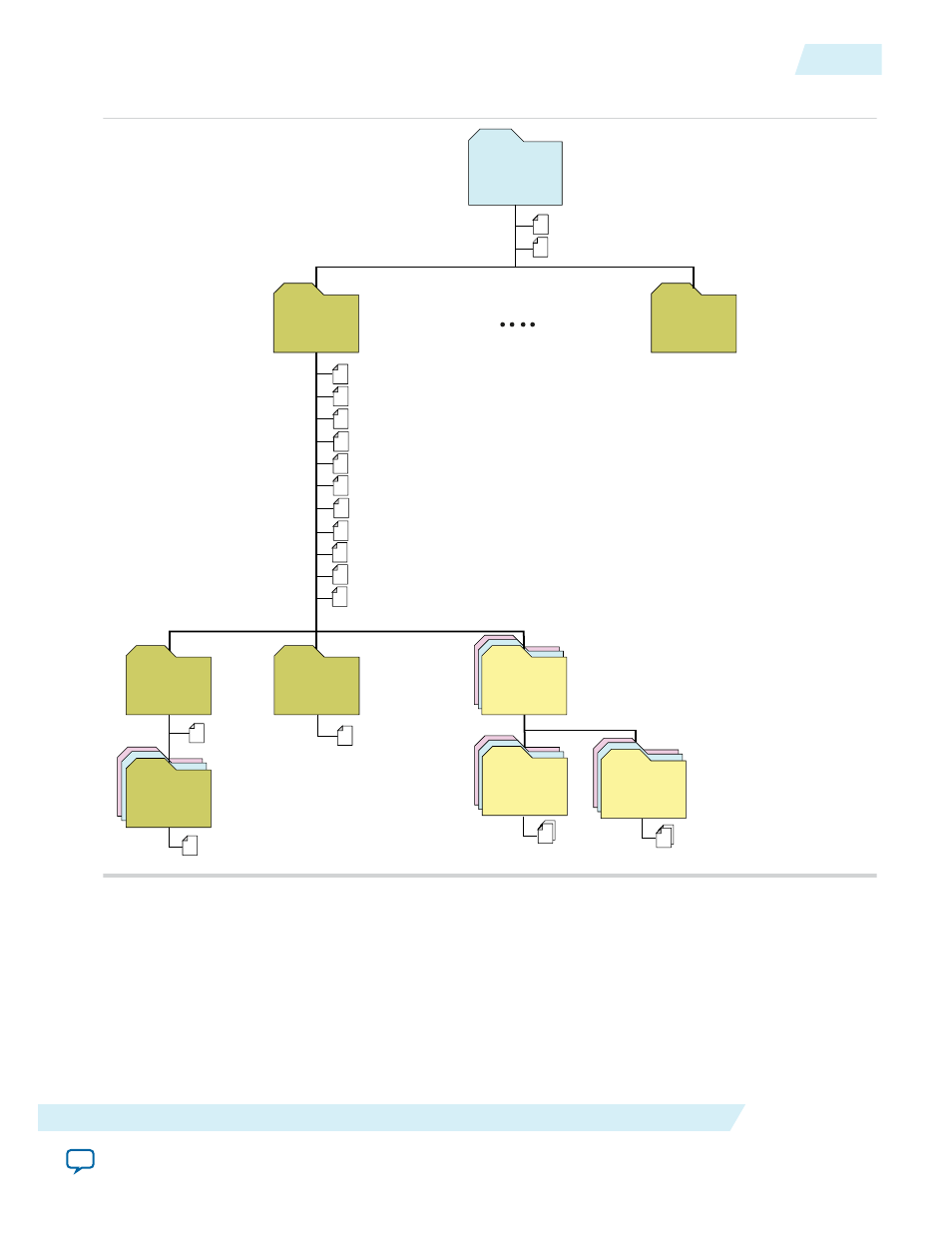

Figure 2-5: IP Core Generated Files

<your_ip >.cmp - VHDL component declaration file

<your_ip >.ppf - XML I/O pin information file

<your_ip >.qip - Lists IP synthesis files

<your_ip >.sip - Lists files for simulation

<your_ip >.v or .vhd

Top-level IP synthesis file

<your_ip >.v or .vhd

Top-level simulation file

<simulator_setup_scripts

>

<your_ip >.qsys - System or IP integration file

<your_ip >_bb.v - Verilog HDL black box EDA synthesis file

<your_ip >_inst.v or .vhd - Sample instantiation template

<your_ip >_generation.rpt - IP generation report

<your_ip >.debuginfo - Contains post-generation information

<your_ip >.html - Connection and memory map data

<your_ip >.bsf - Block symbol schematic

<your_ip >.spd - Combines individual simulation scripts

<your_ip >.sopcinfo - Software tool-chain integration file

<project directory>

<your_ip>

IP variation files

sim

Simulation files

synth

IP synthesis files

<EDA tool name>

Simulator scripts

<ip subcores> n

Subcore libraries

sim

Subcore

Simulation files

synth

Subcore

synthesis files

<HDL files >

<HDL files >

<your_ip> n

IP variation files

Integrating Your IP Core in Your Design

To ensure the HMC Controller IP core functions correctly in hardware, you must connect additional

blocks to your IP core and assign device pins in order.

Pin Constraints

UG-01152

2015.05.04

Integrating Your IP Core in Your Design

2-9

Getting Started with the HMC Controller IP Core

Altera Corporation