4 synchronization clock interface, 3 alarm panel, 4 power inlet – Artesyn Centellis 2000 Shelf - DC Installation and Use (June 2014) User Manual

Page 116

Non-Field-Replaceable Units

Centellis 2000 Shelf - DC Installation and Use (6806800G45F)

116

5.2.4

Synchronization Clock Interface

The complete synchronization clock interface is bussed between the user card and node slots.

It provides a set of clock buses to support applications that require the exchange of

synchronous timing information among multiple boards in a shelf. The synchronization clock

interface path is:

terminator – node slot 1 – user card slot 1 – user card slot 2 – node slot 2 – terminator.

The termination resistors are mounted on the backplane.

The synchronization clock interface is fully compliant to the PICMG 3.0 R3.0 Specification.

Therefore, details are not described within this chapter. For more information, see the PICMG

3.0 R3.0 Specification.

5.3

Alarm Panel

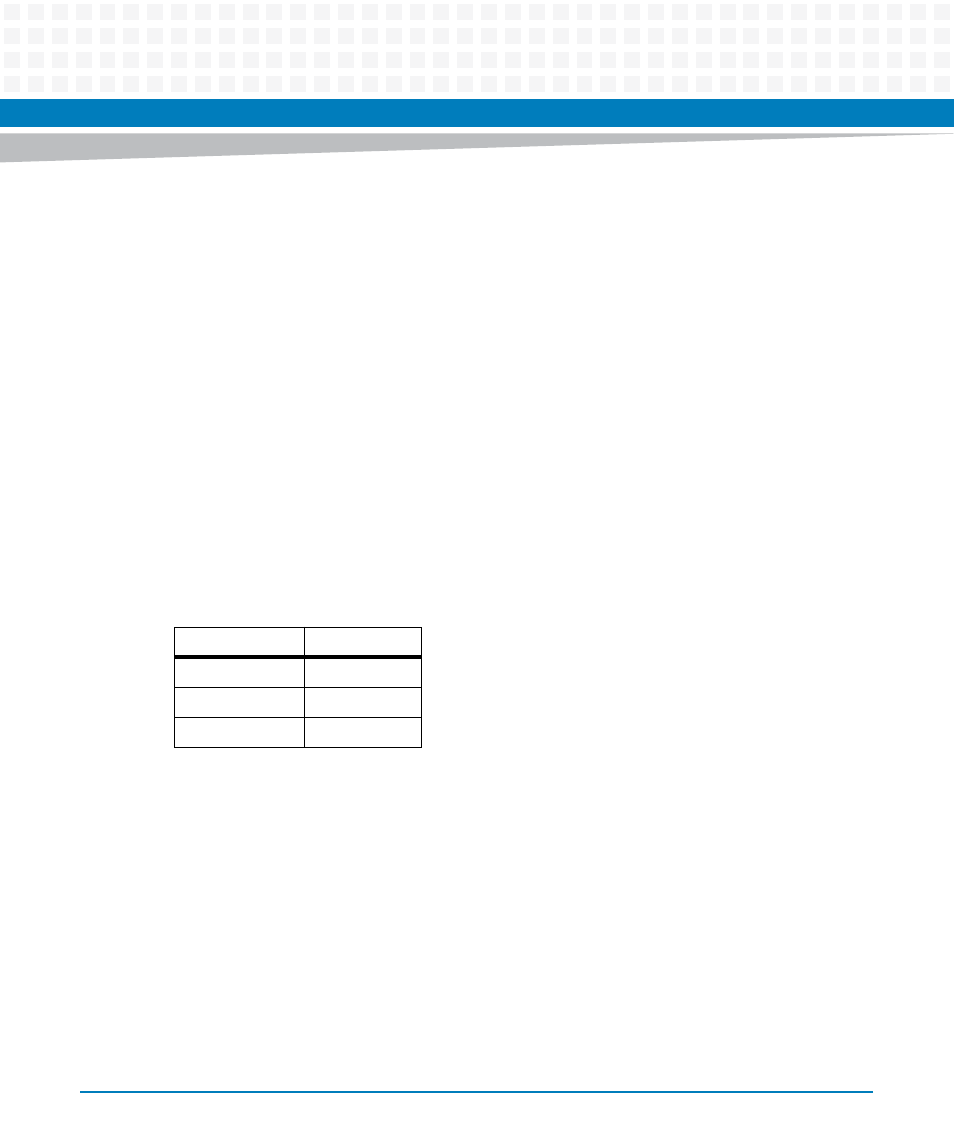

The alarm panel is located on the front of the shelf. It provides LEDs for the following alarm

states of the system:

The signaling is controlled by the system manager via commands via the MF105. The alarm

states are controlled by the system manager.

The alarm panel is fully compliant to the PICMG 3.0 R3.0 Specification.

5.4

Power Inlet

The power inlet is located on the rear of the shelf. It routes the power paths individually from

two high current connectors on the rear of the shelf to two PEM modules that are installed on

the front of the shelf. Pluggable screw terminals are provided to simplify connection.

The power inlet contains a cable harness connecting the DC power input connectors to the

respective PEM input connectors as well as connectivity for safety ground to the PEM.

Alarm State

LED Color

Minor

AMBER

Major

RED

Critical

RED