2 features and registers, 1 features, Features and registers – BECKHOFF ET1200 User Manual

Page 14: Features, Table 4: et1200 feature details, 2features and registers, Availability depending on port configuration

Features and Registers

III-4

Slave Controller

– ET1200 Hardware Description

2

Features and Registers

2.1

Features

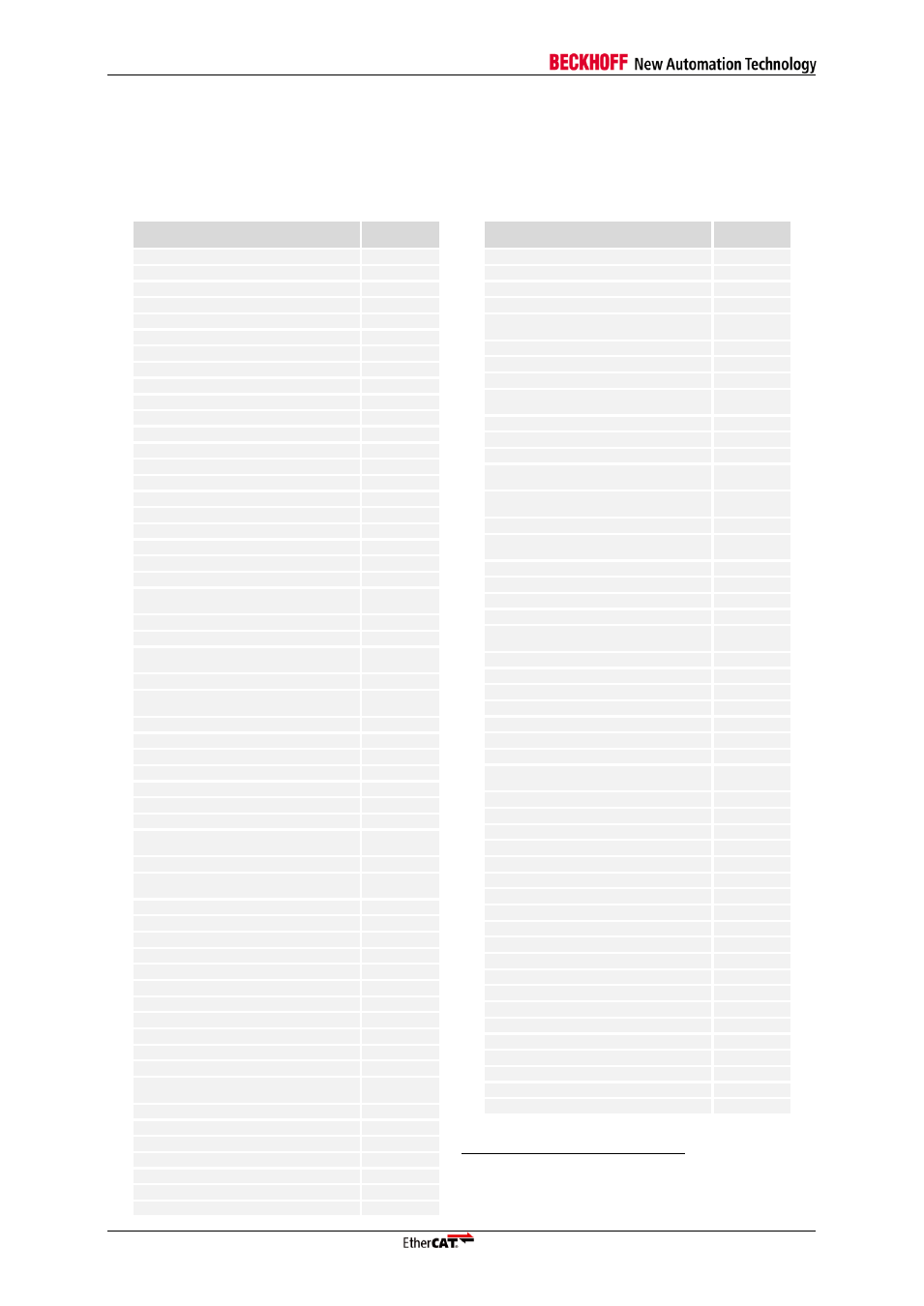

Table 4: ET1200 Feature Details

Feature

ET1200

-0003

EtherCAT Ports

2-3

Permanent ports

2

Optional Bridge port 3 (EBUS or MII)

c

EBUS ports

1-3

MII ports

0-1

RMII ports

-

RGMII ports

-

Port 0

-

Ports 0, 1

x

Ports 0, 1, 2

-

Ports 0, 1, 3

x

Ports 0, 1, 2, 3

-

Slave Category

Full Slave

Position addressing

x

Node addressing

x

Logical addressing

x

Broadcast addressing

x

Physical Layer General Features

FIFO Size configurable (0x0100[18:16])

x

FIFO Size default from SII EEPROM

-

Auto-Forwarder checks CRC and SOF

x

Forwarded RX Error indication, detection

and Counter (0x0308:0x030B)

x

Lost Link Counter (0x0310:0x0313)

x

Prevention of circulating frames

x

Fallback: Port 0 opens if all ports are

closed

x

VLAN Tag and IP/UDP support

x

Enhanced Link Detection per port

configurable

-

EBUS Features

Low Jitter

x

Enhanced Link Detection supported

-

Enhanced Link Detection compatible

X

EBUS signal validation

X

LVDS Transceiver internal

X

LVDS sample rate [MHz]

1,000

Remote link down signaling time

configurable 0x0100[22]

x

General Ethernet Features (MII/RMII/RGMII)

MII Management Interface

(0x0510:0x051F)

x

Supported PHY Address Offsets

0/16

Individual port PHY addresses

-

Port PHY addresses readable

-

Link Polarity configurable

-

Enhanced Link Detection supported

x

FX PHY support (native)

-

PHY reset out signals

-

Link detection using PHY signal (LED)

x

MI link status and configuration

-

MI controllable by PDI (0x0516:0x0517)

-

MI read error (0x0510.13)

-

MI PHY configuration update status

(0x0518.5)

-

MI preamble suppression

-

Additional MCLK

x

Gigabit PHY configuration

-

Gigabit PHY register 9 relaxed check

-

FX PHY configuration

-

Transparent Mode

-

Feature

ET1200

-0003

MII Features

CLK25OUT as PHY clock source

x

Bootstrap TX Shift settings

x

Automatic TX Shift setting (with TX_CLK)

-

TX Shift not necessary (PHY TX_CLK as

clock source)

-

FIFO size reduction steps

1

PDI General Features

Increased PDI performance

-

Extended PDI Configuration

(0x0152:0x0153)

x

PDI Error Counter (0x030D)

-

PDI Error Code (0x030E)

-

CPU_CLK output (10, 20, 25 MHz)

x

SOF, EOF, WD_TRIG and WD_STATE

independent of PDI

-

Available PDIs and PDI features

depending on port configuration

x

PDI selection at run-time (SII EEPROM)

x

PDI active immediately (SII EEPROM

settings ignored)

-

PDI function acknowledge by write

-

PDI Information register 0x014E:0x014F

-

Digital I/O PDI

x

Digital I/O width [bits]

8/16

PDI Control register value

(0x0140:0x0141)

4

Control/Status signals:

2/0

1,2

LATCH_IN

SOF

OUTVALID

WD_TRIG

OE_CONF

-

OE_EXT

-

EEPROM_

Loaded

-

WD_STATE

-

EOF

-

Granularity of direction configuration [bits]

2

Bidirectional mode

x

Output high-Z if WD expired

x

Output 0 if WD expired

-

Output with EOF

x

Output with DC SyncSignals

x

Input with SOF

x

Input with DC SyncSignals

x

1

Shared control/status signals: LATCH_IN/SOF and

OUT_VALID/WD_TRIGGER

2

Availability depending on port configuration