4 port 0/1 and pdi[17:8] signals, Port 0/1 and pdi[17:8] signals – BECKHOFF ET1200 User Manual

Page 29

Pin Description

Slave Controller

– ET1200 Hardware Description

III-19

CPU_CLK

The ET1200 can provide a clock signal for µControllers on pin PDI[7]/CPU_CLK. The CPU_CLK

output setting is controlled by the CLK_MODE configuration pin. If CPU_CLK is enabled, PDI[7] is not

available for the PDI, i.e., I/O[7] is not available for Digital I/O PDI.

CPU_CLK provides a clock signal

– if configured – during external or ECAT reset, clock output is only

turned off during power-on reset.

3.7.4

Port 0/1 and PDI[17:8] Signals

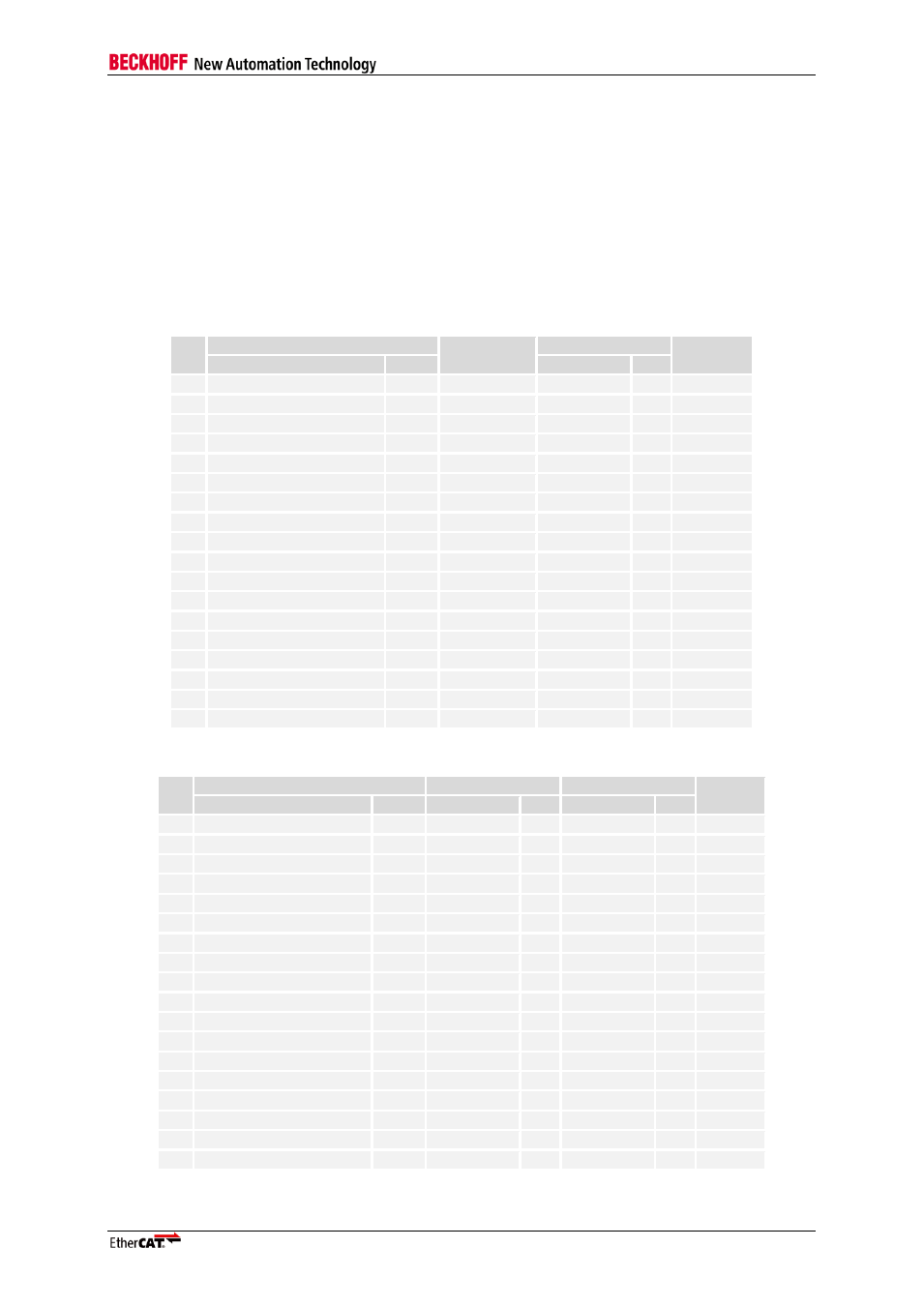

Table 22 and Table 23 show the port 0/1 and PDI signals used for ports 0 and 1.

Table 22: Port 0/1 and PDI signals (Configuration and chip mode 00)

Pin

Pin

Configuration

MODE[1:0]=00

Internal

PU/PD

Name

Dir

Signal

Dir.

36

PDI[8]/TX_D[0]/PHYAD_OFF

BD

PHYAD_OFF

PDI[8]

BD

35

PDI[9]/TX_D[1]/C25_ENA

BD

C25_ENA

PDI[9]

BD

34

PDI[10]/TX_D[2]/C25_SHI[0]

BD

C25_SHI[0]

PDI[10]

BD

33

PDI[11]/TX_D[3]/C25_SHI[1]

BD

C25_SHI[1]

PDI[11]

BD

32

PDI[12]/RX_CLK

BD

PDI[12]

BD

31

PDI[13]/RX_DV

BD

PDI[13]

BD

30

PDI[14]/RX_D[0]

BD

PDI[14]

BD

29

PDI[15]/RX_D[1]

BD

PDI[15]

BD

28

PDI[16]/RX_D[2]

BD

PDI[16]

BD

27

PDI[17]/RX_D[3]

BD

PDI[17]

BD

2

EBUS{1}-RX-/LINK_MII

LI-/I

EBUS(1)-RX-

LI-

27 k

Ω PU

3

EBUS{1}-RX+/RX_ERR

LI+/I

EBUS(1)-RX+

LI+

27 k

Ω PD

10

EBUS{1}-TX-/MI_CLK

LO-/O

EBUS(1)-TX-

LO-

11

EBUS{1}-TX+/TX_ENA

LO+/O

EBUS(1)-TX+

LO+

8

EBUS{0}-RX-

LI-

EBUS(0)-RX-

LI-

27 k

Ω PU

9

EBUS{0}-RX+

LI+

EBUS(0)-RX+

LI+

27 k

Ω PD

4

EBUS{0}-TX-

LO-

EBUS(0)-TX-

LO-

5

EBUS{0}-TX+

LO+

EBUS(0)-TX+

LO+

Table 23: Port 0/1 and PDI signals (chip modes 10/11)

Pin

Pin

MODE[1:0]=10

MODE[1:0]=11

Internal

PU/PD

Name

Dir

Signal

Dir.

Signal

Dir.

36

PDI[8]/TX_D[0]/PHYAD_OFF

BD

TX_D(0)[0]

O

TX_D(1)[0]

O

35

PDI[9]/TX_D[1]/C25_ENA

BD

TX_D(0)[1]

O

TX_D(1)[1]

O

34

PDI[10]/TX_D[2]/C25_SHI[0]

BD

TX_D(0)[2]

O

TX_D(1)[2]

O

33

PDI[11]/TX_D[3]/C25_SHI[1]

BD

TX_D(0)[3]

O

TX_D(1)[3]

O

32

PDI[12]/RX_CLK

BD

RX_CLK(0)

I

RX_CLK(1)

I

31

PDI[13]/RX_DV

BD

RX_DV(0)

I

RX_DV(1)

I

30

PDI[14]/RX_D[0]

BD

RX_D(0)[0]

I

RX_D(1)[0]

I

29

PDI[15]/RX_D[1]

BD

RX_D(0)[1]

I

RX_D(1)[1]

I

28

PDI[16]/RX_D[2]

BD

RX_D(0)[2]

I

RX_D(1)[2]

I

27

PDI[17]/RX_D[3]

BD

RX_D(0)[3]

I

RX_D(1)[3]

I

2

EBUS{1}-RX-/LINK_MII

LI-/I

LINK_MII(0)

I

LINK_MII(1)

I

27 k

Ω PU

3

EBUS{1}-RX+/RX_ERR

LI+/I

RX_ERR(0)

I

RX_ERR(1)

I

27 k

Ω PD

10

EBUS{1}-TX-/MI_CLK

LO-/O

MI_CLK

O

MI_CLK

O

11

EBUS{1}-TX+/TX_ENA

LO+/O

TX_ENA(0)

O

TX_ENA(1)

O

8

EBUS{0}-RX-

LI-

EBUS(1)-RX-

LI-

EBUS(0)-RX-

LI-

27 k

Ω PU

9

EBUS{0}-RX+

LI+

EBUS(1)-RX+

LI+

EBUS(0)-RX+

LI+

27 k

Ω PD

4

EBUS{0}-TX-

LO-

EBUS(1)-TX-

LO-

EBUS(0)-TX-

LO-

5

EBUS{0}-TX+

LO+

EBUS(1)-TX+

LO+

EBUS(0)-TX+

LO+