3 general et1200 pins, 4 sii eeprom interface pins, General et1200 pins – BECKHOFF ET1200 User Manual

Page 25: Sii eeprom interface pins, Table 17: general pins, Table 18: sii eeprom pins

Pin Description

Slave Controller

– ET1200 Hardware Description

III-15

3.3

General ET1200 Pins

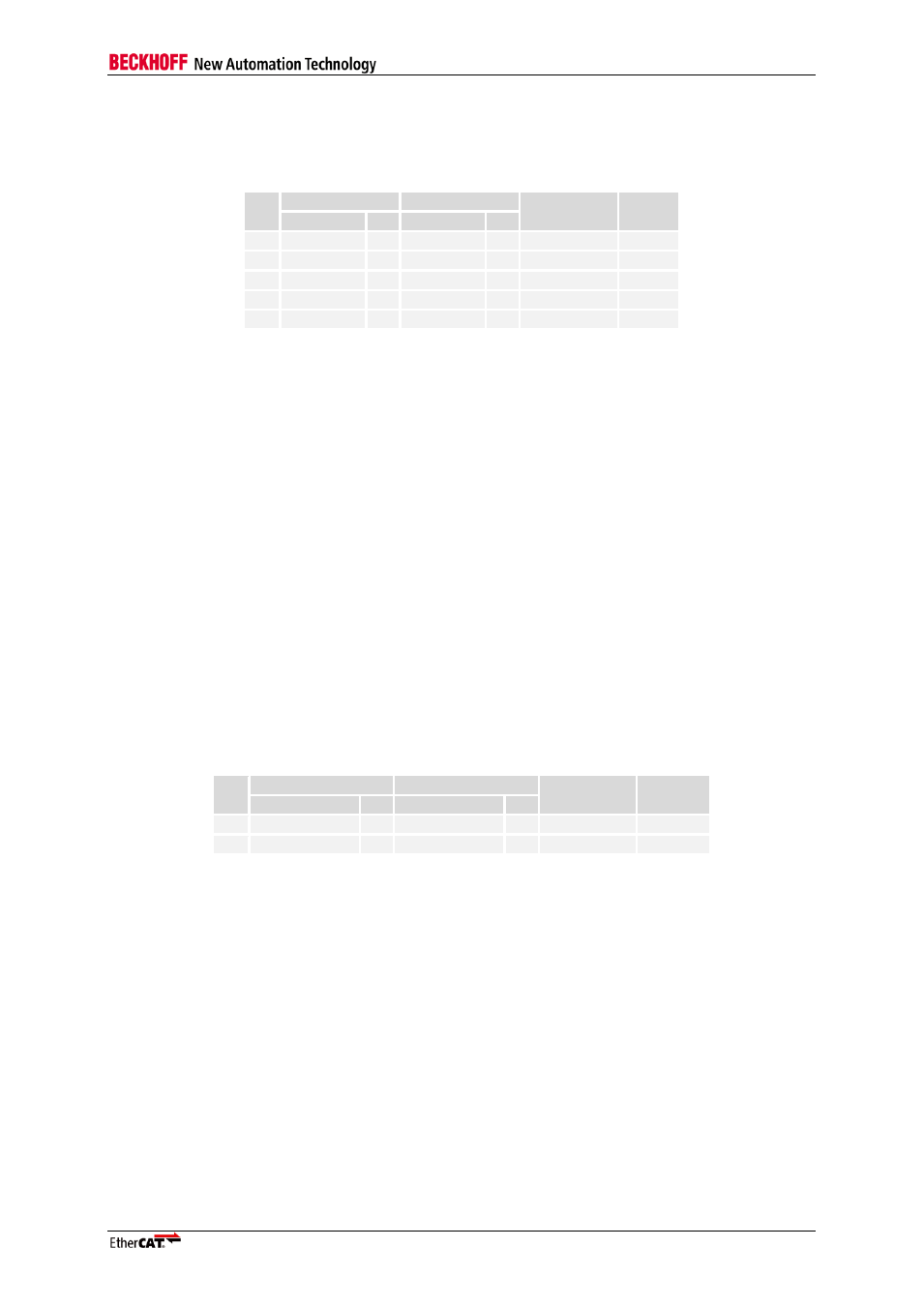

Table 17: General pins

Pin

Pin

Signal

Configuration

Internal

PU/PD

Name

Dir

Name

Dir

21

OSC_IN

I

OSC_IN

I

22

OSC_OUT

O

OSC_OUT

O

26

RESET

BD

RESET

BD

WPU

25

RBIAS

RBIAS

1

TESTMODE

I

TESTMODE

I

WPD

OSC_IN

Connection to external crystal or oscillator input (25 MHz). An oscillator as the clock source for both

ET1200 and the Ethernet PHY is mandatory if an MII port is used and CLK25OUT cannot be used as

the clock source for the PHY. The 25 MHz clock source should have an initial accuracy of 25ppm or

better.

OSC_OUT

Connection to external crystal. Should be left open if an oscillator is connected to OSC_IN.

RESET

The open collector RESET input/output (active low) signals the reset state of ET1200. The reset state

is entered at power-on, if the power supply is to low, or if a reset was initiated using the reset register

0x0040. ET1200 also enters reset state if RESET pin is held low by external devices.

RBIAS

Bias resistor for LVDS TX current adjustment, should be 11 k

Ω connected to GND.

TESTMODE

Reserved for testing, should be connected to GND.

3.4

SII EEPROM Interface Pins

Table 18: SII EEPROM pins

Pin

Pin

Signal

Configuration

Internal

PU/PD

Name

Dir

Name

Dir

19

EEPROM_CLK

BD

EEPROM_CLK

BD

3.3 k

Ω PU

20

EEPROM_DATA

BD

EEPROM_DATA

BD

3.3 k

Ω PU

EEPROM_CLK

EEPROM I²C clock signal (open collector output).

EEPROM_DATA

EEPROM I²C data signal (open collector output).