Nonburst opcode fetch, 32-bit address and data – Avago Technologies LSI53C1010R User Manual

Page 312

Advertising

6-22

Specifications

Version 2.2

Copyright © 2000–2003 by LSI Logic Corporation. All rights reserved.

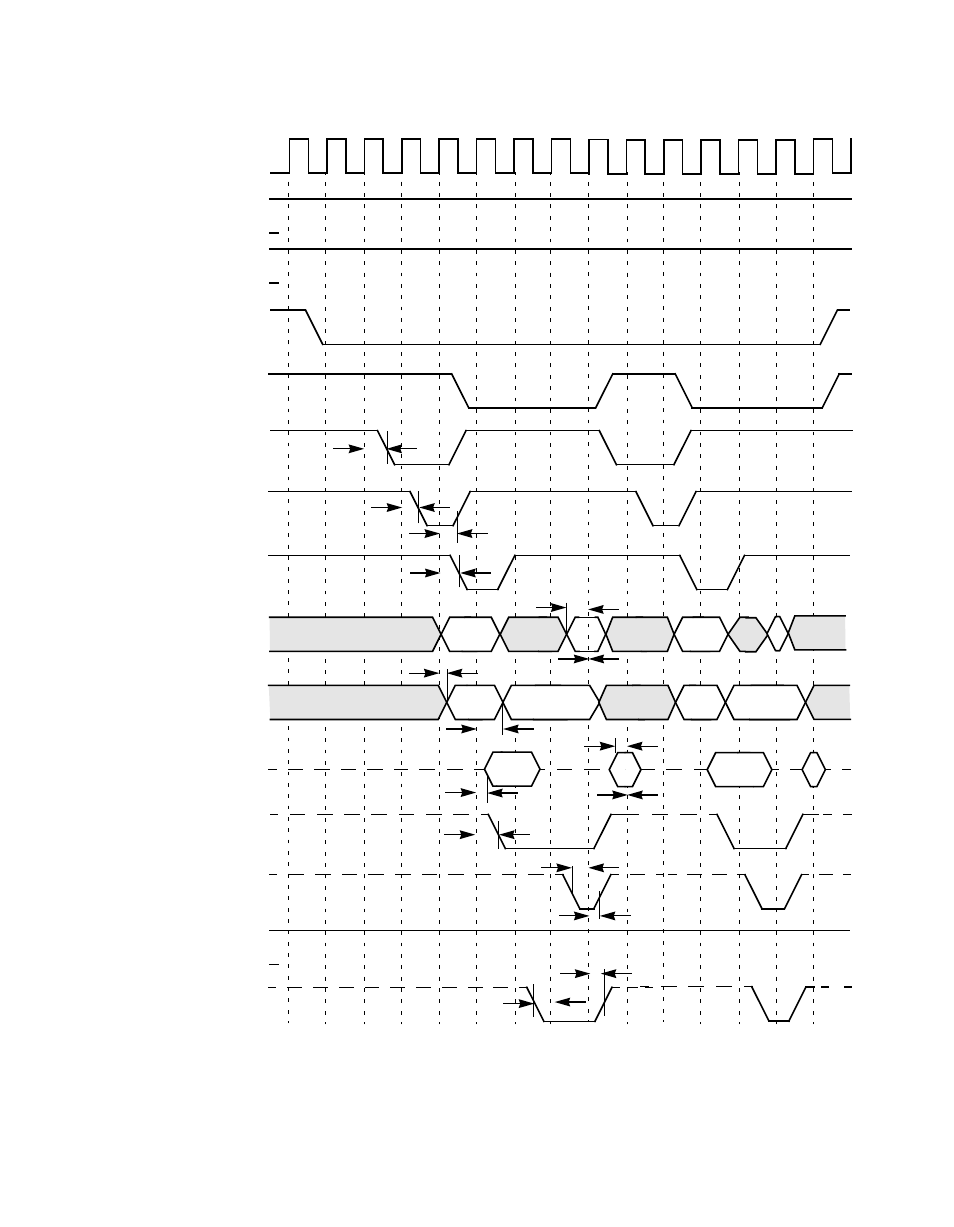

Figure 6.17 Nonburst Opcode Fetch, 32-Bit Address and Data

t

3

t

4

t

1

t

3

t

1

CLK

(Driven by System)

GPIO0_FETCH/

(Driven by LSI53C1010R)

GPIO1_MASTER/

(Driven by LSI53C1010R)

REQ/

(Driven by LSI53C1010R)

PAR

(Driven by LSI53C1010R-

IRDY/

(Driven by LSI53C1010R)

TRDY/

(Driven by Target)

STOP/

(Driven by Target)

DEVSEL/

(Driven by Target)

t

1

t

6

t

3

AD[31:0]

(Driven by LSI53C1010R-

C_BE[3:0]/

(Driven by LSI53C1010R)

t

3

CMD

t

2

REQ64/

(Driven by LSI53C1010R)

ACK64/

(Driven by LSI53C1010R)

t

1

t

2

GNT/

(Driven by Arbiter)

FRAME/

(Driven by LSI53C1010R)

t

5

Data

In

Addr

Out

Data

In

Addr

Out

Byte

Enable

CMD

Byte

Enable

t

3

t

2

t

2

Addr; Target-Data)

Addr; Target-Data)

Advertising