Avago Technologies LSI53C1010R User Manual

Page 56

2-26

Functional Description

Version 2.2

Copyright © 2000–2003 by LSI Logic Corporation. All rights reserved.

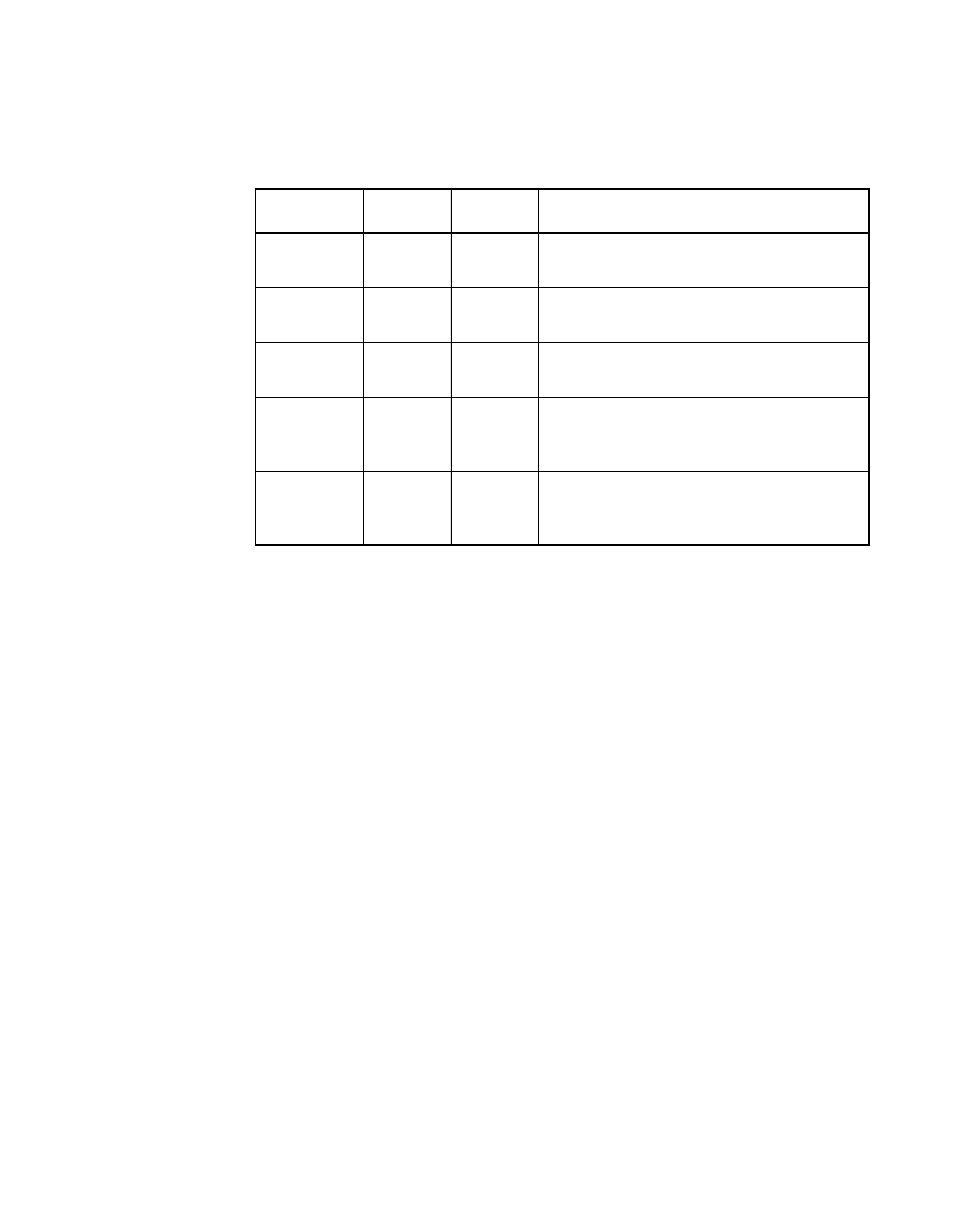

Protocol Options (Byte 7) – A bus or device reset, power cycle, or

change between LVD/SE modes invalidates these settings. A

renegotiation resets the Protocol Options.

2.2.5.3 Asynchronous Information Protection (AIP)

The AIP feature provides error checking for asynchronous, nondata

phases through BCH encoding. During the command, status, message

in/out phases, the BCH code is transferred on the upper SCSI data bus.

For details on the BCH code, refer to the T10 119 document, “Protection

for the Asynchronous Phases”.

The AIP error status and the live AIP code values are captured in the

register for debug purposes. AIP checking

is enabled by setting bit 6 in the

register.

AIP generation occurs by default and may be disabled by setting bit 3,

Disable AIP Code Generation, in

The sequence ID is reset on any phase change, chip reset, bus free, or

synchronous phase. It is also reset by writing the RAIPERR bit in the

register.

All AIP errors are treated in the same fashion as parity errors. Bit 0 of the

SCSI Interrupt Status Zero (SIST0)

register indicates if SCSI parity, CRC,

or AIP errors are present. The AIPERR bit in the

register indicates if the error is an AIP error.

QAS_REQ

DT_REQ

IU_REQ

Description

0

0

0

Use ST Data-In and ST Data-Out phase

to transfer data.

0

1

0

Use DT Data-In and DT Data-Out phase

to transfer data with CRC.

0

1

1

Use DT Data-In and DT Data-Out phase

to transfer data with information units.

1

1

0

Use DT Data-In and DT Data-Out phase

to transfer data with CRC and use the

QAS method for arbitration.

1

1

1

Use DT Data-In and DT Data-Out phase

to transfer data with information units and

use the QAS method for arbitration.