Clocking modes and clock enable, Clocking modes and clock enable -6 – Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 16

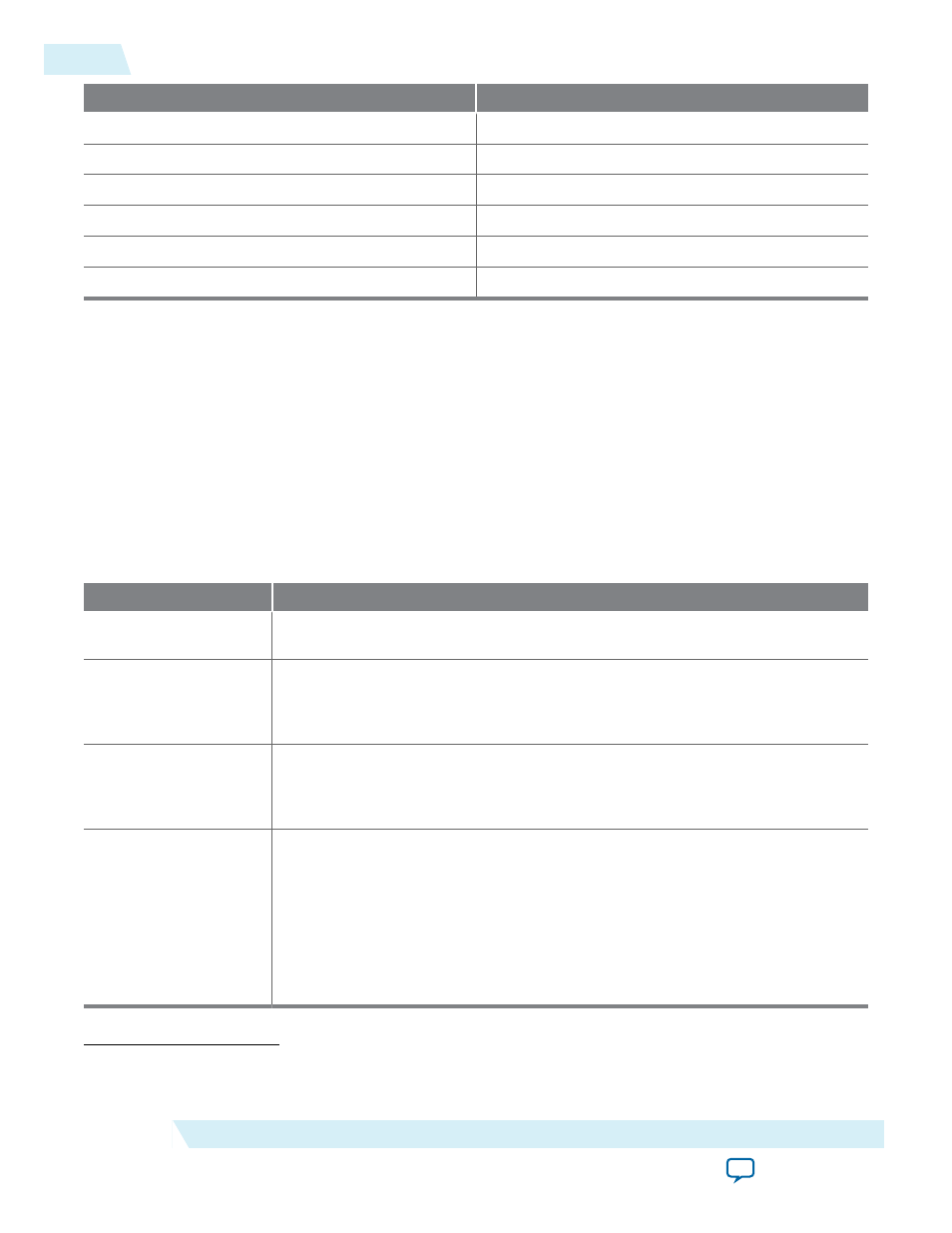

Embedded Memory Blocks

Valid Range

(6)

M144K

2K–16K

M9K

256–8K

MLAB

32–64

(7)

M512

32–512

M4K

128–4K

M-RAM

4K–64K

The parameter editor prompts an error message if you enter an invalid value for the maximum block

depth. Altera recommends that you set the value to Auto if you are not sure of the appropriate maximum

block depth to set or the setting is not important for your design. This setting enables the compiler to

select the maximum block depth with the appropriate port width configuration for the type of embedded

memory block of your memory.

Clocking Modes and Clock Enable

The embedded memory block supports various types of clocking modes depending on the memory mode

you select.

Table 3-4: Clocking Modes

Clocking Modes

Description

Single Clock Mode

In the single clock mode, a single clock, together with a clock enable, controls all

registers of the memory block.

Read/Write Clock

Mode

In the read/write clock mode, a separate clock is available for each read and write

port. A read clock controls the data-output, read-address, and read-enable

registers. A write clock controls the data-input, write-address, write-enable, and

byte enable registers.

Input/Output Clock

Mode

In input/output clock mode, a separate clock is available for each input and

output port. An input clock controls all registers related to the data input to the

memory block including data, address, byte enables, read enables, and write

enables. An output clock controls the data output registers.

Independent Clock

Mode

In the independent clock mode, a separate clock is available for each port (A and

B). Clock A controls all registers on the port A side; clock B controls all registers

on the port B side.

Note: You can create independent clock enable for different input and

output registers to control the shut down of a particular register for

power saving purposes. From the parameter editor, click More

Options (beside the clock enable option) to set the available

independent clock enable that you prefer.

(6)

The maximum block depth must be in a power of two.

(7)

The maximum block depth setting (64) for MLAB is not available for Arria V and Cyclone V devices.

3-6

Clocking Modes and Clock Enable

UG-01068

2014.12.17

Altera Corporation

Embedded Memory Functional Description