Port ip core -2 – Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 48

is asserted. Because the RAM mode has two dedicated write ports, another encoder is implemented for the

other RAM input port.

Two ALTECC_DECODER blocks are also implemented at each of the data output ports of the RAM.

When the read-enable signal is asserted, the encoded data is read from the RAM address and decoded by

the ALTECC_DECODER blocks, respectively. The decoder shows the status of the data as no error

detected, single-bit error detected and corrected, or fatal error (more than 1-bit error).

This example also includes a "corrupt zero bit" control signal at port A of the RAM. When the signal is

asserted, it changes the state of the zero-bit (LSB) encoded data before it is written into the RAM. This

signal is used to corrupt the zero-bit data storing through port A, and examines the effect of the ECC

features.

This design example describes how ECC features can be implemented with the RAM for cases in which

the ECC is not supported internally by the RAM. However, the design examples might not represent the

optimized design or implementation.

Generating the ALTECC_ENCODER and ALTECC_DECODER with the RAM: 2-PORT IP

Core

To generate the ALTECC_ENCODER and ALTECC_DECODER with the RAM: 2-PORT IP core, follow

these steps:

1. Open the Internal_Memory_DesignExample.zip file and extract true_dp.qar.

2. In the Quartus II software, open the true_dp.qar file and restore the archive file into your working

directory.

3. In the IP Catalog (Tools > IP Catalog), locate and double-click the ALTECC IP core. The parameter

editor appears.

4. Specify the following parameters:

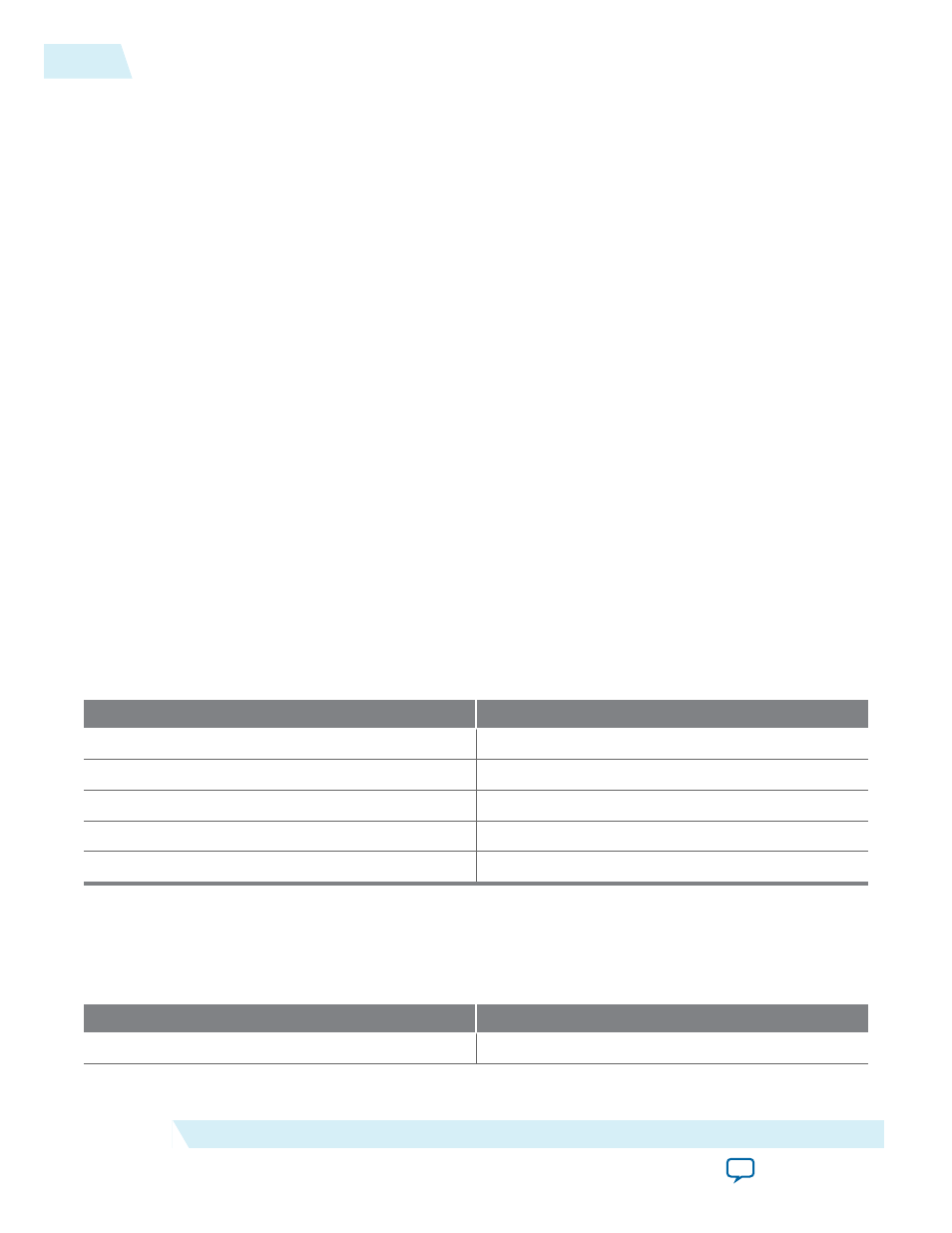

Table 5-1: Configuration Settings for ALTECC_ENCODER

Option

Value

How do you want to configure this module?

Configure this module as an ECC encoder

How wide should the data be?

8 bits

Do you want to pipeline the functions?

Yes, I want an output latency of 1 clock cycle

Create an 'aclr' asynchronous clear port

Not selected

Create a 'clocken' clock enable clock

Not selected

5. Click Finish. The ecc_encoder.v module is built.

6. In the IP Catalog double-click the ALTECC IP core. The parameter editor appears.

7. Specify the following parameters:

Table 5-2: Configuration Settings for ALTECC_DECODER

Option

Value

How do you want to configure this module?

Configure this module as an ECC decoder

5-2

Generating the ALTECC_ENCODER and ALTECC_DECODER with the RAM: 2-PORT IP

Core

UG-01068

2014.12.17

Altera Corporation

Design Example