Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 36

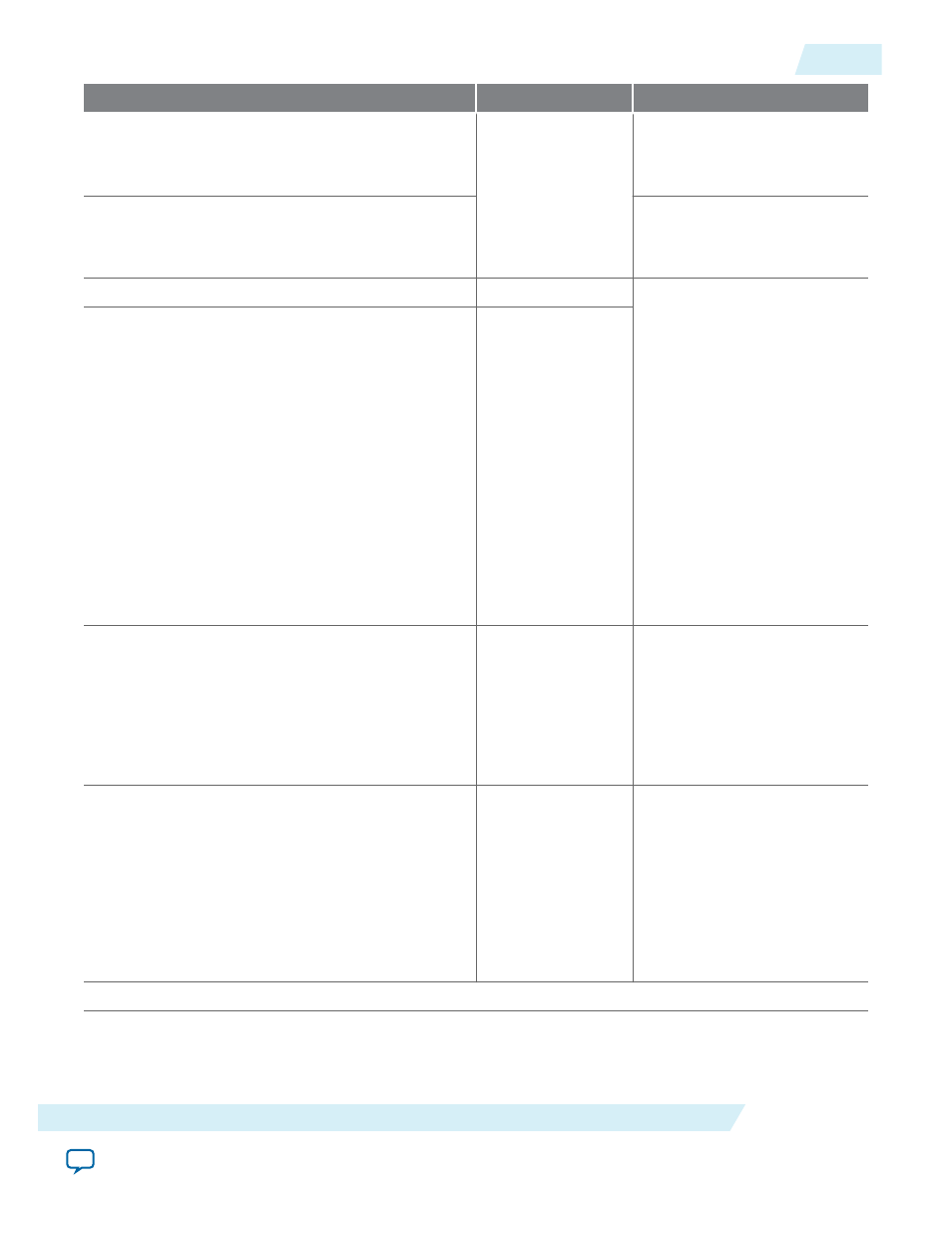

Parameter

Legal Values

Description

When you select With one read port and one write

port, the following option is available:

Create a ‘rden’ read enable signal

—

Specifies whether to create a

read enable signal for port B.

When you select With two read/write ports, the

following option is available:

Create a ‘rden_a’ and ‘rden_b’ read enable signal

Specifies whether to create a

read enable signal for port A

and B.

Create byte enable for port A

—

Specifies whether to create a

byte enable for port A and B.

Turn on these options if you

want to mask the input data

so that only specific bytes,

nibbles, or bits of data are

written.

To enable byte enable for

port A and port B, the data

width ratio has to be 1 or 2

for the RAM: 1-PORT and

RAM: 2-PORT IP cores.

The option to create a byte

enable for port B is only

available when you select the

With two read/write ports

option.

Create byte enable for port B

—

Enable error checking and correcting (ECC) to

check and correct single bit errors and detect double

errors

On/Off

Specifies whether to enable

the ECC feature that corrects

single bit errors and detects

double errors at the output

of the memory. This option

is only available in devices

that support M144K memory

block type.

Enable error checking and correcting (ECC) to

check and correct single bit errors, double adjacent

bit errors, and detect triple adjacent bit errors

On/Off

Specifies whether to enable

the ECC feature that corrects

single bit errors, double

adjacent bit errors, and

detects triple adjacent bit

errors at the output of the

memory. This option is only

available in devices that

support M20K memory

block type.

Parameter Settings: Regs/Clkens/Aclrs

UG-01068

2014.12.17

RAM: 2-Port IP Core Parameters

4-11

Embedded Memory Signals and Parameters

Altera Corporation