Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 57

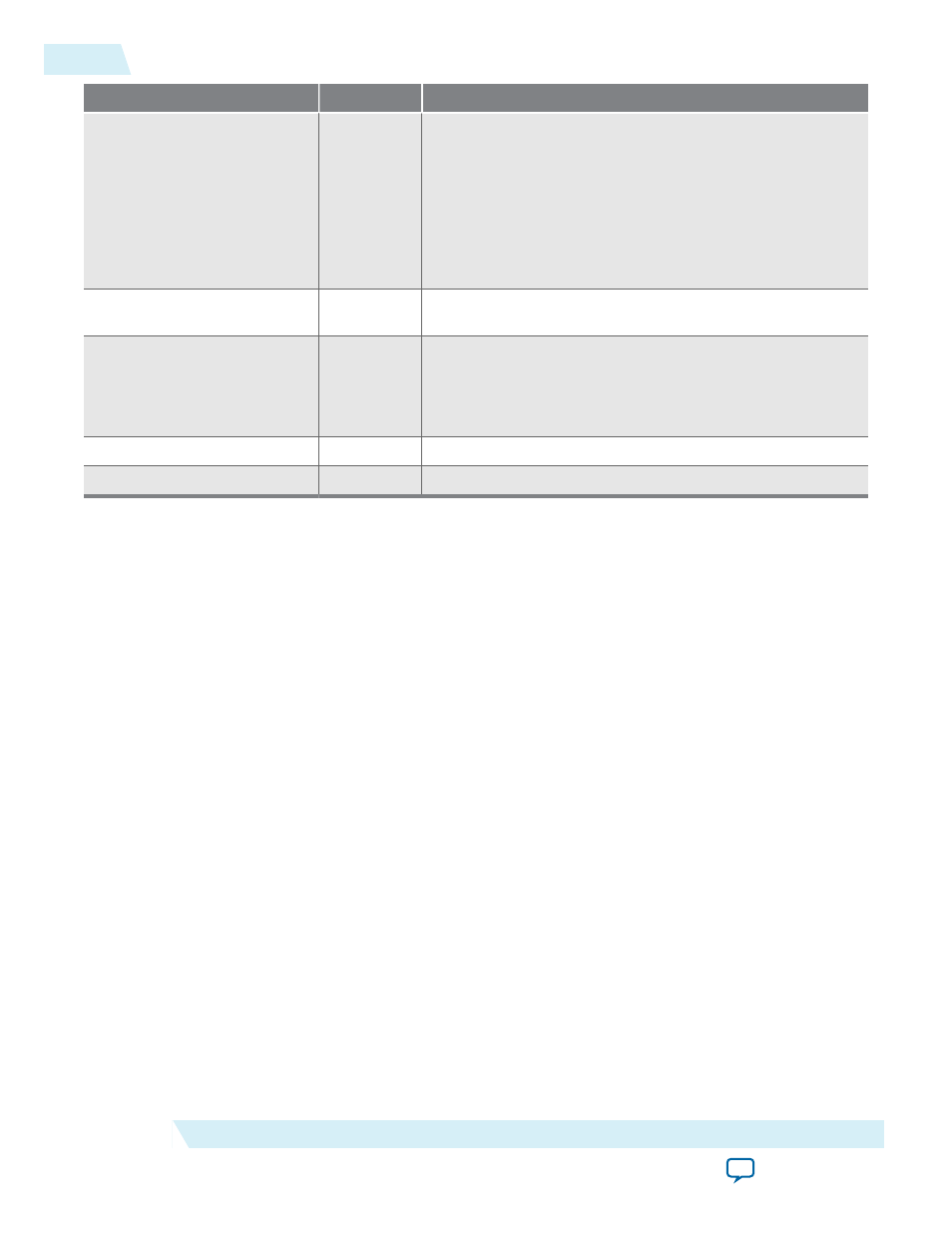

Date

Version

Changes

November 2012

4.1

• Added a note to the “Asynchronous Clear” on page 3–15

to state that internal contents cannot be cleared with the

asynchronous clear signal.

• Updated note in “Clocking Modes and Clock Enable” on

page 3–11 to include Stratix V devices.

• Added a note to the “Asynchronous Clear” on page 3–15

to clarify that clear deassertion on output latch is

dependent on output clock.

January 2012

4.0

Added a note to “Power-Up Conditions and Memory

Initialization” section.

November 2011

3.0

• Updated the RAM2:Port parameter settings.

• Updated the Read-During-Write section. Added M10K

memory block information.

• Added support information for Arria V and Cyclone V.

March 2011

2.0

Added new features for M20K memory block.

November 2009

1.0

Initial release

A-2

Document Revision History

UG-01068

2014.12.17

Altera Corporation

Document Revision History