Simulating the design, Simulation results – Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 50

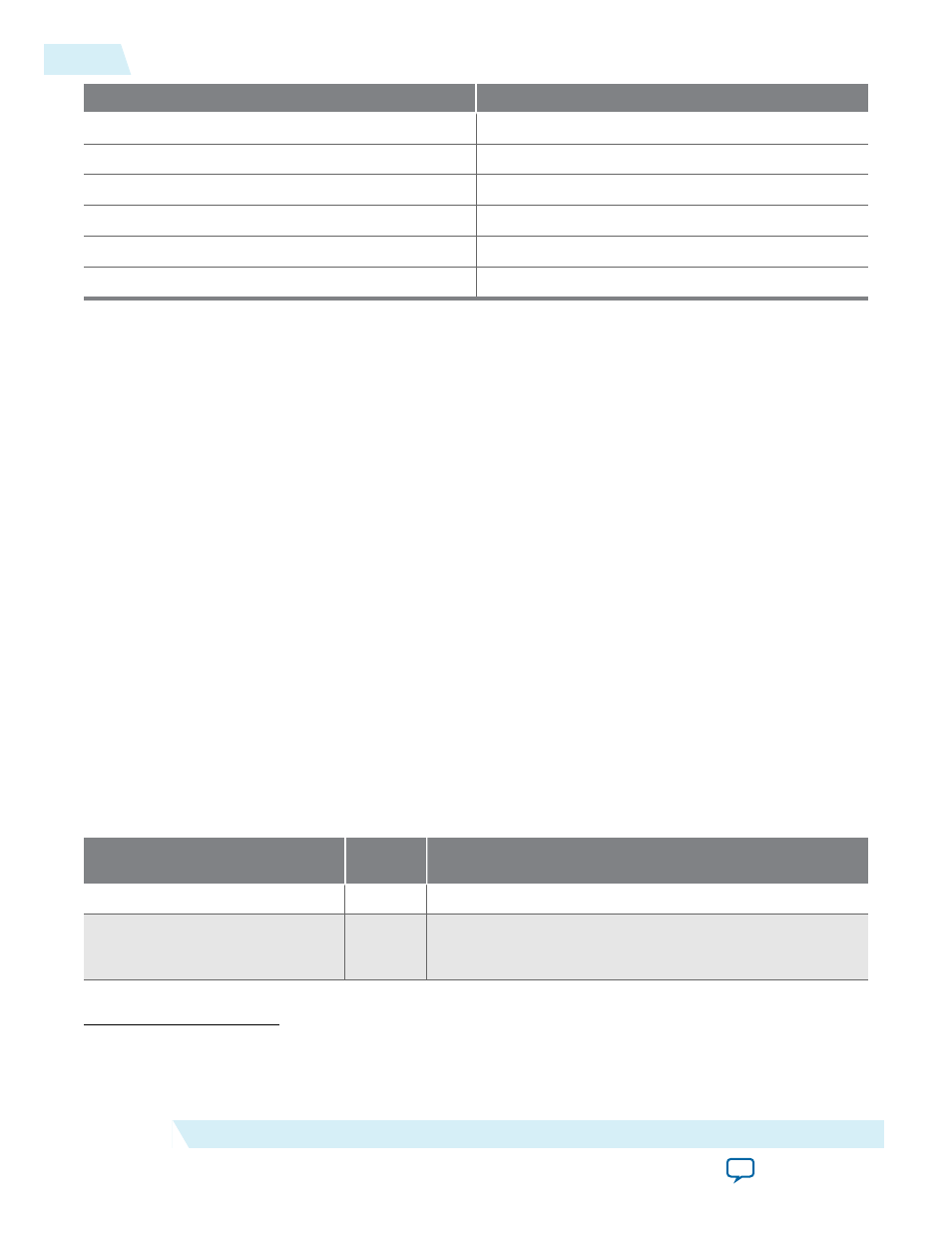

Option

Value

Generate netlist

Turned off

Variation file (.vhd)

Turned on

AHDL Include file (.inc)

Turned off

VHDL component declaration file (.cmp)

Turned on

Quartus II symbol file (.bsf)

Turned off

Instantiation template file(.vhd)

Turned off

11.Click Finish. The true_dp_ram.v module is built.

The top_dpram.v is a design variation file that contains the top level file that instantiates two encoders, a

true dual-port RAM, and two decoders. To simulate the design, a testbench, true_dp_ram.vt, is created

for you to run in the ModelSim-Altera software.

Simulating the Design

To simulate the design in the ModelSim-Altera software, follow these steps:

1. Unzip the Internal_Memory_DesignExample.zip file to any working directory on your PC.

2. Start the ModelSim-Altera software.

3. On the File menu, click Change Directory.

4. Select the folder in which you unzipped the files.

5. Click OK.

6. On the Tools menu, point to TCL and click Execute Macro. The Execute Do File dialog box appears.

7. Select the true_dp.do file and click Open. The true_dp.do file is a script file that automates all the

necessary settings, compiles and simulates the design files, and displays the simulation waveform.

8. Verify the result shown in the Waveform Viewer window.

You can rearrange signals, remove signals, add signals, and change the radix by modifying the script in

true_dp.do accordingly.

Simulation Results

This table lists the top-level block contains the input and output ports.

Table 5-4: Top-level Input and Output Ports Representations

Ports Name

Ports

Type

Descriptions

clock

Input

System Clock for the encoders, RAM, and decoders.

corrupt_dataa_bit0

Input

Registered active high control signal that 'twist' the zero bit

(LSB) of input encoded data at port A before writing into

the RAM.

(17)

(17)

For input ports, only data signal goes through the encoder; others bypass the encoder and go directly to

the RAM block. Because the encoder uses one pipeline, signals that bypass the encoder require additional

pipelines before going to the RAM. This has been implemented in the top level.

5-4

Simulating the Design

UG-01068

2014.12.17

Altera Corporation

Design Example