Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 30

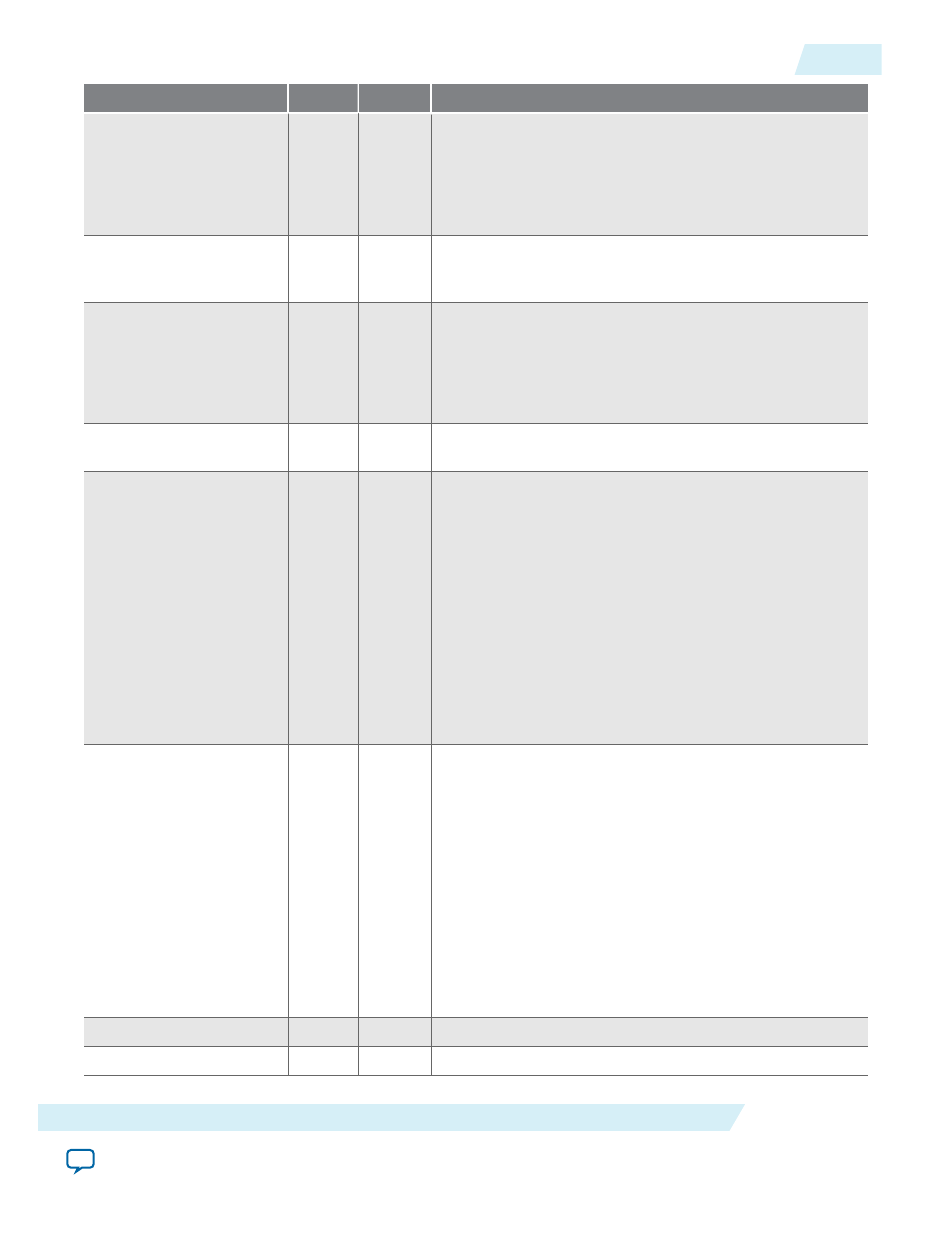

Signal

Type

Required

Description

byteena

Input Optional Byte enable input to mask the data port so that only

specific bytes, nibbles, or bits of data are written. The

byteena

port is not supported when

use_eab

parameter is

set to

OFF

. It is supported in Arria II GX, Stratix III,

Cyclone III, and newer devices with the

ram_block_type

parameter set to MLAB.

wraddressstall

Input Optional Write address clock enable input to hold the previous

write address of

wraddress

port for as long as the

wraddressstall

port is high.

rdaddressstall

Input Optional Read address clock enable input to hold the previous read

address of

rdaddress

port for as long as the

wraddress-

stall

port is high. The

rdaddressstall

port is only

supported in Stratix II, Cyclone II, Arria GX, and newer

devices except when the

rdaddress_reg

parameter is set

to

UNREGISTERED.

q

Output

Yes

Data output from the memory. The

q

port is required, and

must be equal to the width data port.

inclock

Input

Yes

The following describes which of your memory clock must

be connected to the

inclock

port, and port synchroniza‐

tion in different clocking modes:

• Single clock: Connect your single source clock to

inclock

port and

outclock

port. All registered ports

are synchronized by the same source clock.

• Read/Write: Connect your write clock to

inclock

port.

All registered ports related to write operation, such as

data

port,

wraddress

port,

wren

port, and

byteena

port are synchronized by the write clock.

• Input/Output: Connect your input clock to

inclock

port. All registered input ports are synchronized by the

input clock.

outclock

Input

Yes

The following describes which of your memory clock must

be connected to the

outclock

port, and port synchroniza‐

tion in different clocking modes:

• Single clock: Connect your single source clock to

inclock

port and

outclock

port. All registered ports

are synchronized by the same source clock.

• Read/Write: Connect your read clock to

outclock

port. All registered ports related to read operation, such

as

rdaddress

port,

rdren

port, and

q

port are

synchronized by the read clock.

• Input/Output: Connect your output clock to

outclock

port. The registered

q

port is synchronized by the

output clock.

inclocken

Input Optional Clock enable input for

inclock

port.

outclocken

Input Optional Clock enable input for

outclock

port.

UG-01068

2014.12.17

Signals

4-5

Embedded Memory Signals and Parameters

Altera Corporation