Asynchronous clear, Read enable, Asynchronous clear -10 – Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 20: Read enable -10

Asynchronous Clear

The embedded memory blocks in the Arria II GX, Arria II GZ, Stratix IV, Stratix V, and newer device

families support the asynchronous clear feature used on the output latches and output registers.

Therefore, if your RAM does not use output registers, clear the RAM outputs using the output latch

asynchronous clear. The asynchronous clear feature allows you to clear the outputs even if the q output

port is not registered. However, this feature is not supported in MLAB memory blocks.

The outputs stay cleared until the next clock. However, in Arria V, Cyclone V, and Stratix V devices, the

outputs stay cleared until the next read.

Note: You cannot use the asynchronous clear port to clear the contents of the embedded memory. Use

the asynchronous clear port to clear the contents of the input and output register stages only.

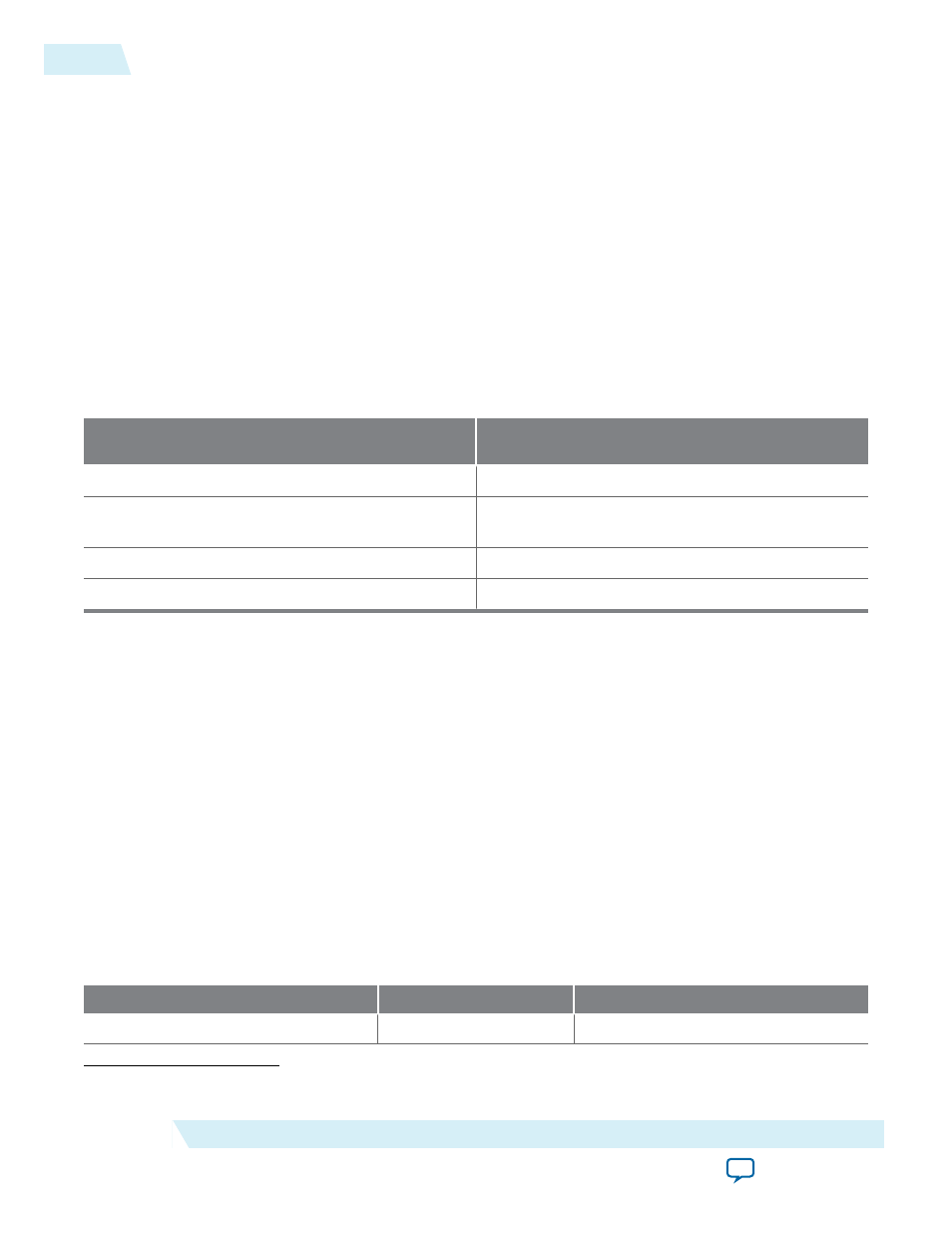

Table 3-6: Asynchronous Clear Effects on the Input Ports for Various Devices in Various Memory Settings

This table lists the asynchronous clear effects on the input ports for various devices in various memory settings.

Memory Mode

Arria II GX, Arria II GZ, Arria V, Cyclone V, Stratix IV,

Stratix V, and newer devices

Single-port RAM

All registered input ports are not affected.

(8)

Single dual-port RAM and True dual-port RAM

Only registered input read address port can be

affected.

Single-port ROM

Registered input address port can be affected.

Dual-port ROM

All registered input ports are not affected.

Note: During a read operation, clearing the input read address asynchronously corrupts the memory

contents. The same effect applies to a write operation if the write address is cleared.

Note: Beginning from Arria V, Cyclone V, and Stratix V devices onwards, an output clock signal is

needed to successfully recover the output latch from an asynchronous clear signal. This implies

that in a single clock mode true dual-port RAM, setting clock enabled on the registered output may

affect the recovery of the unregistered output because they share the same output clock signal. To

avoid this, provide an output clock signal (with clock enabled) to the output latch to deassert an

asynchronous clear signal from the output latch.

Read Enable

Support for the read enable feature depends on the target device, memory block type, and the memory

mode you select.

Table 3-7: Read-Enable Support in Various Device Families

This table lists the memory configurations for various device families that support the read enable feature.

Memory Modes

M9K, M144K, M10K, M20K

MLAB

Single-port RAM

Supported

—

(8)

When LCs are implemented in this memory mode, registered output port is not affected.

3-10

Asynchronous Clear

UG-01068

2014.12.17

Altera Corporation

Embedded Memory Functional Description