Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 35

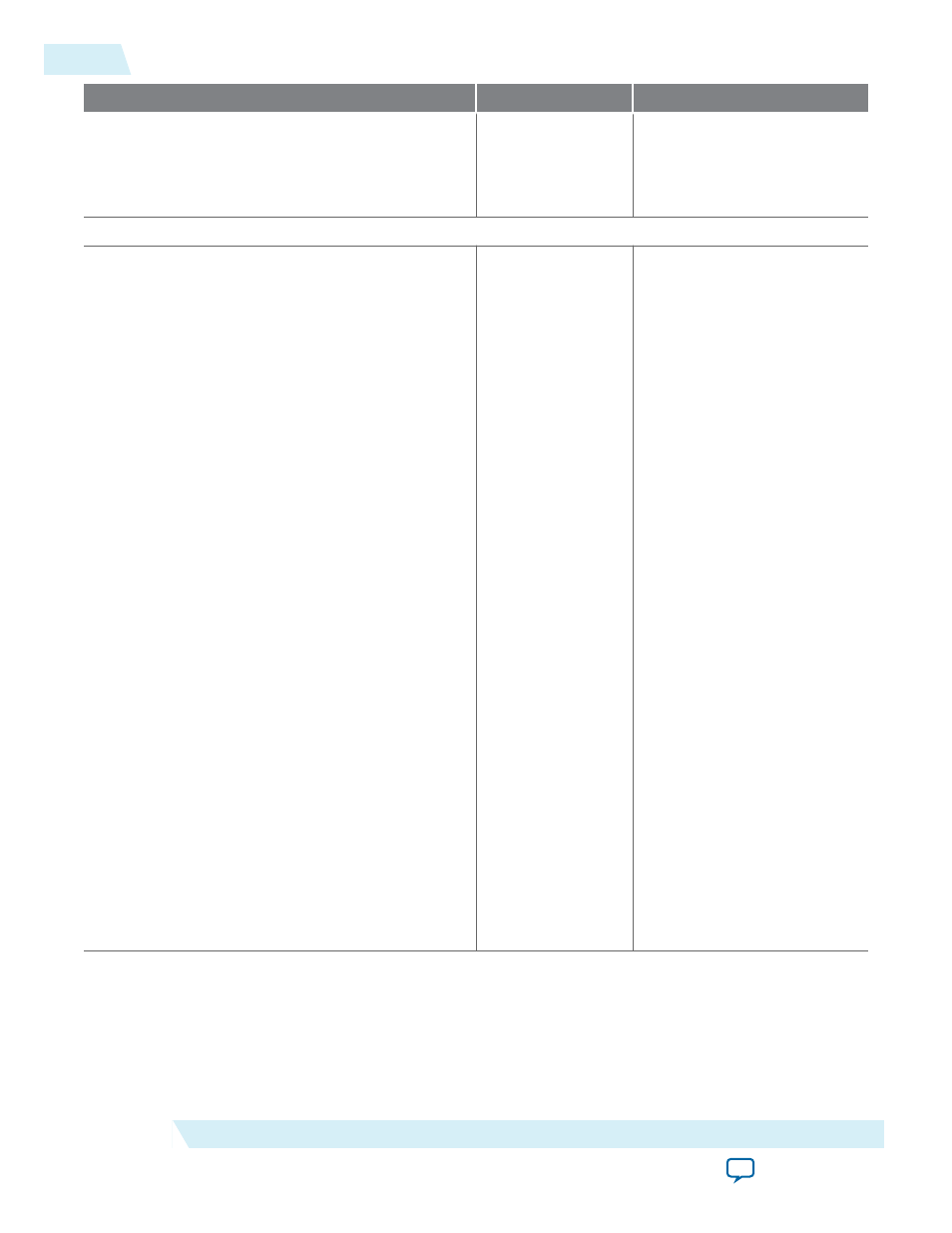

Parameter

Legal Values

Description

Set the maximum block depth to

Auto, 32, 64, 128,

256, 512, 1024, 2048,

4096

Specifies the maximum block

depth in words. This option

is enabled only when you set

the memory block type to

Auto.

Parameter Settings: Clks/Rd, Byte En

What clocking method would you like to use?

When you select

With one read port

and one write port,

the following values

are available:

•

Single clock

•

Dual clock: use

separate ‘input’

and ‘output’

clocks

•

Dual clock: use

separate ‘read’

and ‘write’ clock

When you select

With two read/write

ports, the following

options are available:

•

Single clock

•

Dual clock: use

separate ‘input’

and ‘output’

clocks

•

Dual clock: use

separate clocks

for A and B ports

Specifies the clocking

method to use.

• Single clock—A single

clock and a clock enable

controls all registers of

the memory block.

• Dual Clock: use separate

‘input’ and ‘output’

clocks—An input and an

output clock controls all

registers related to the

data input and output to/

from the memory block

including data, address,

byte enables, read enables,

and write enables.

• Dual clock: use separate

‘read’ and ‘write’ clock—

A write clock controls the

data-input, write-address,

and write-enable registers

while the read clock

controls the data-output,

read-address, and read-

enable registers.

• Dual clock: use separate

clocks for A and B ports

—Clock A controls all

registers on the port A

side; clock B controls all

registers on the port B

side. Each port also

supports independent

clock enables for both

port A and port B

registers, respectively.

4-10

RAM: 2-Port IP Core Parameters

UG-01068

2014.12.17

Altera Corporation

Embedded Memory Signals and Parameters