Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 54

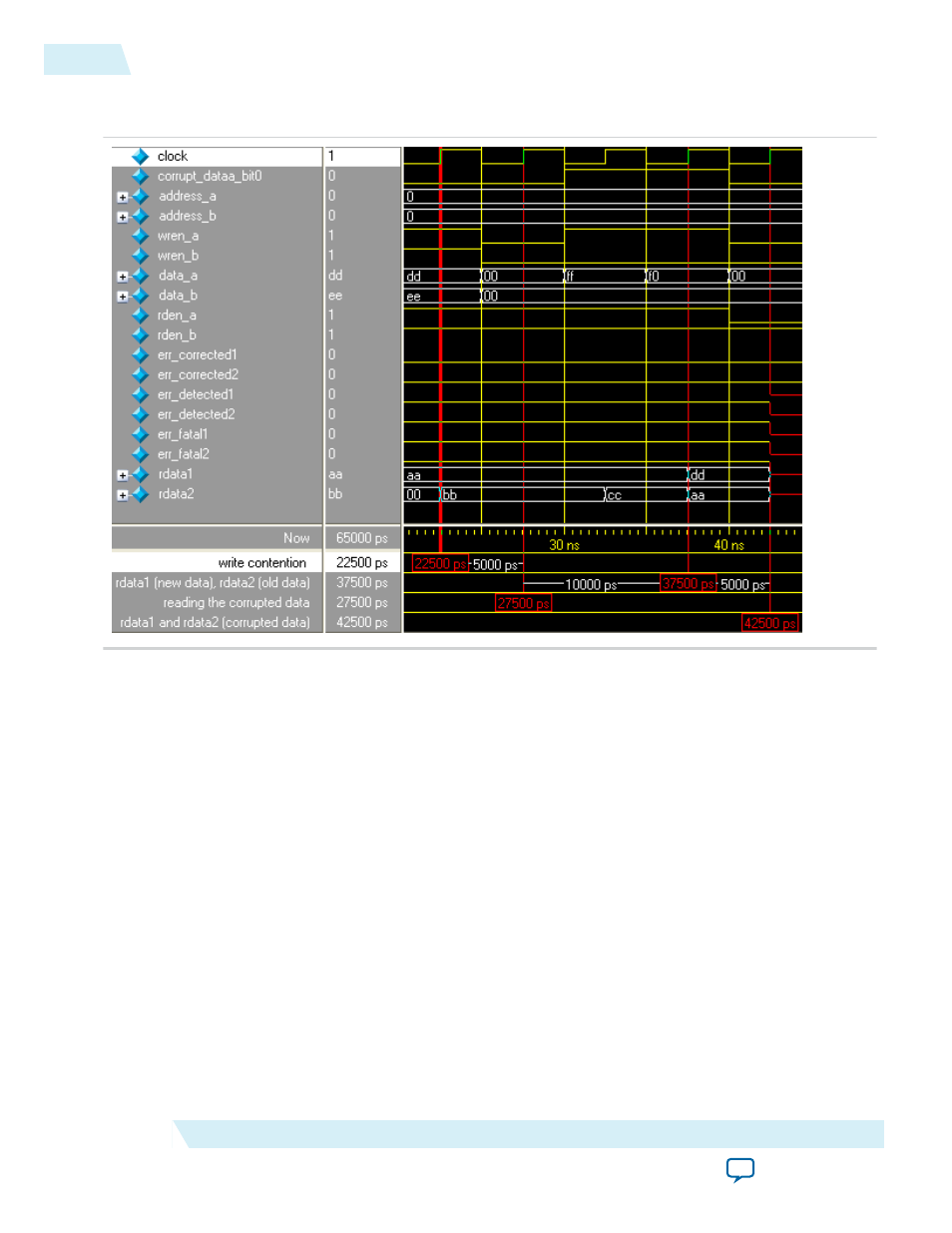

Figure 5-4: Write Contention

This figure shows the timing diagram of when the write contention occurs.

At 22500 ps, the write contention occurs when data

dd

and

ee

are written to address 0 simultaneously.

Besides that, the same-port read-during-write also occurs for port A and port B. The setting for port A

and port B for same-port read-during-write takes effect when the

rdata1

port shows the new data

dd

and

the

rdata2

port shows the old data

aa

after four clock cycles at 37500 ps. When the data is read again

from the same address at the next rising clock edge at 27500 ps,

rdata1

and

rdata2

ports show unknown

values at 42500 ps. Apart from that, the unknown data input to the decoder also results in an unknown

ECC status.

5-8

Simulation Results

UG-01068

2014.12.17

Altera Corporation

Design Example