Altera Stratix IV E FPGA Development Board User Manual

Page 31

Chapter 2: Board Components

2–23

Clock Circuitry

May 2011

Altera Corporation

Stratix IV E FPGA Development Board Reference Manual

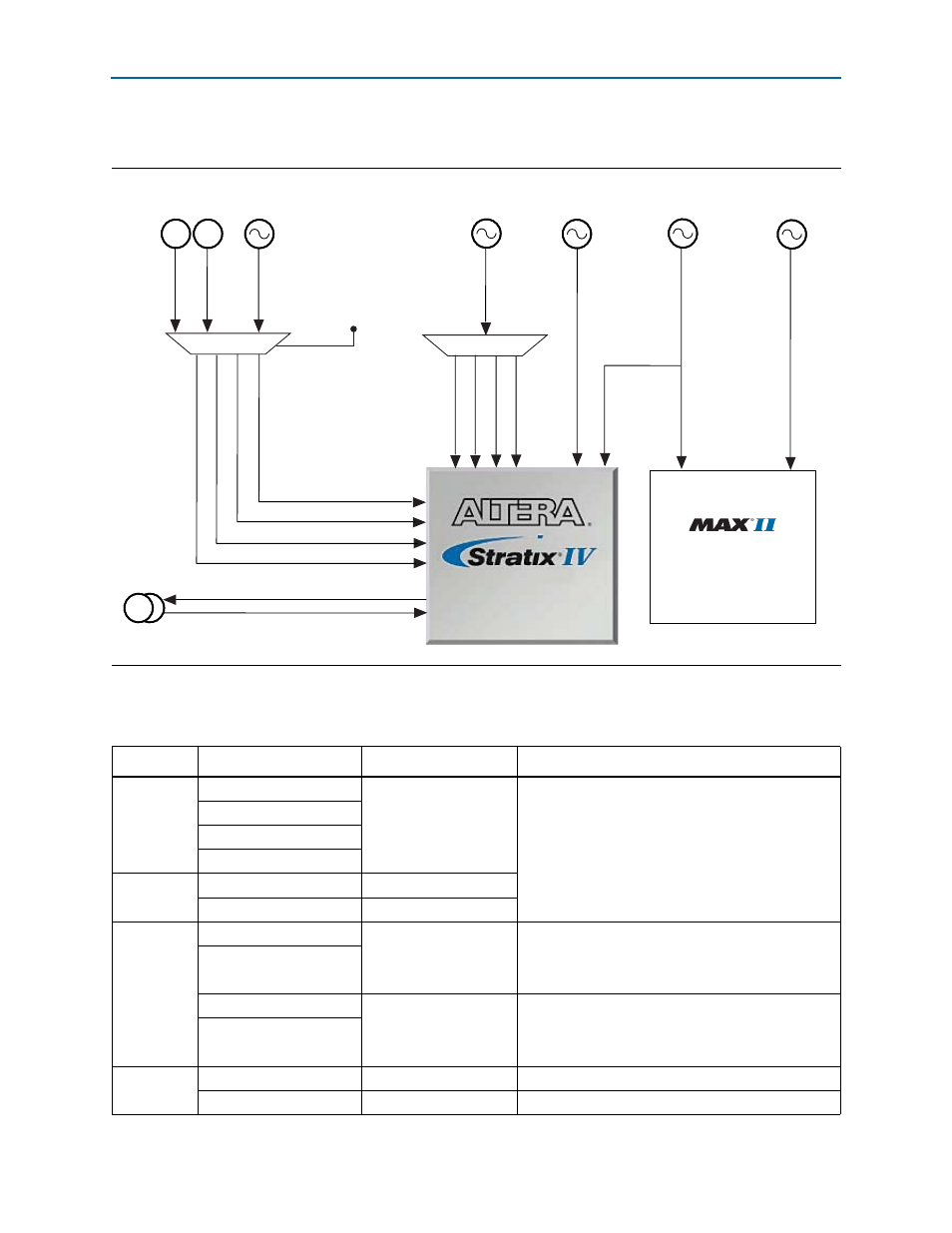

shows the Stratix IV E FPGA development board clocking diagram.

shows the clock distribution for the Stratix IV E FPGA development board.

Figure 2–6. Stratix IV E FPGA Development Board Clocking Diagram

LVDS

EP4SE530H35

EPM2210F256

CPLD

CLK66_SEL (SW2)

CLKIN_66M_P0

CLKOUT_SMA

Clock Buffer

Clock Buffer

66.6 MHz SMT

Oscillator

SMA

SMA

SMA

SMA

LVDS

CLKIN_50

CLKIN_MAX_100

LVPECL

LVPECL

LVPECL

125.0 MHz SMT

Oscillator

50.0 MHz SMT

Oscillator

100.0 MHz SMT

Oscillator

100.0 MHz SMT

Oscillator

CLKIN_66M_N0

CLKIN_66M_P1

CLKIN_66M_N1

CLKIN_SMA

CLKIN_125M_P0

CLKIN_125M_N0

CLKIN_125M_P1

CLKIN_125M_N1

Table 2–22. Stratix IV E FPGA Development Board Clock Distribution (Part 1 of 2)

Frequency

Schematic Signal Name

Signal Originates From

Signal Propagates To

66.6 MHz

CLKIN_66M_P0

X3.3

U19.W33

U19.W34

U19.AN16

U19.AP16

(From clock buffer, IDT ICS8543, U22)

CLKIN_66M_N0

CLKIN_66M_P1

CLKIN_66M_N1

User Input

CLKIN_SMA_P

J13

CLKIN_SMA_N

J14

125.00 MHz

CLKIN_125M_P0

X4.4

U19.T33

U19.B16

(From clock buffer NB6L11SMNG, U40)

CLKIN_125M_P1

CLKIN_125M_N0

X4.5

U19.T34

U19.A16

(From clock buffer NB6L11SMNG, U40)

CLKIN_125M_N1

100.00 MHz

CLKIN_100M_P0

X2.4

U19.B17

CLKIN_100M_N0

X2.5

U19.A17