Altera Cyclone IV GX FPGA Development Board User Manual

Page 44

2–36

Chapter 2: Board Components

Components and Transceiver Interfaces

Cyclone IV GX FPGA Development Board

May 2013

Altera Corporation

Reference Manual

J2.151

CMOS bit 74

HSMB_T_TX_D_N16

2.5-V

—

U36.18

J2.152

CMOS bit 75

HSMB_T_RX_D_N16

—

U37.12

J2.155

CMOS bit 76

HSMB_T_CLK_OUT_P2

—

U34.3

J2.156

CMOS bit 77

HSMBT_CLK_IN_P2

—

U33.4

J2.157

CMOS bit 78

HSMB_CLK_OUT_N2

Y25

—

J2.158

CMOS clock in 2 or CMOS bit 79

HSMB_CLK_IN_N2

V28

—

J2.160

HSMC Port B presence detect

HSMB_PSNTn

C26

U7.H2;R2.1

D6

User LED to show RX data activity

on HSMC Port B

HSMB_RX_LED

C10

D6.2

D5

User LED to show TX data activity

on HSMC Port B

HSMB_TX_LED

D25

D5.2

—

—

HSMAT_CLK_IN0

A15

U32.3

—

Dedicated CMOS clock in

HSMB_CLK_IN_P2

1.8-V

AG22

U33.3

—

Dedicated CMOS clock out

HSMB_CLK_OUT_P2

AG19

U34.4

—

—

HSMB_RX_D_N6

AE19

U38.5

—

—

HSMB_RX_D_N7

AJ25

U38.9

—

—

HSMB_RX_D_N8

Y20

U38.8

—

—

HSMB_RX_D_N9

AE17

U37.4

—

—

HSMB_RX_D_N10

AA20

U38.7

—

—

HSMB_RX_D_N11

AK19

U37.7

—

—

HSMB_RX_D_N12

AG20

U38.3

—

—

HSMB_RX_D_N13

AD10

U29.4

—

—

HSMB_RX_D_N14

AF18

U38.2

—

—

HSMB_RX_D_N15

AG3

U28.4

—

—

HSMB_RX_D_N16

AD16

U37.9

—

—

HSMB_RX_D_P6

AE20

U38.4

—

—

HSMB_RX_D_P7

AG23

U38.6

—

—

HSMB_RX_D_P8

AK20

U37.6

—

—

HSMB_RX_D_P9

AJ19

U37.5

—

—

HSMB_RX_D_P10

AE16

U37.3

—

—

HSMB_RX_D_P11

AG17

U37.2

—

—

HSMB_RX_D_P12

AG18

U37.8

—

—

HSMB_RX_D_P13

AG16

U29.9

—

—

HSMB_RX_D_P14

AH3

U28.6

—

—

HSMB_RX_D_P15

AK13

U28.5

—

Management serial data

HSMB_SCL

K22

U39.5

—

Management serial clock

HSMB_SDA

F10

U39.4

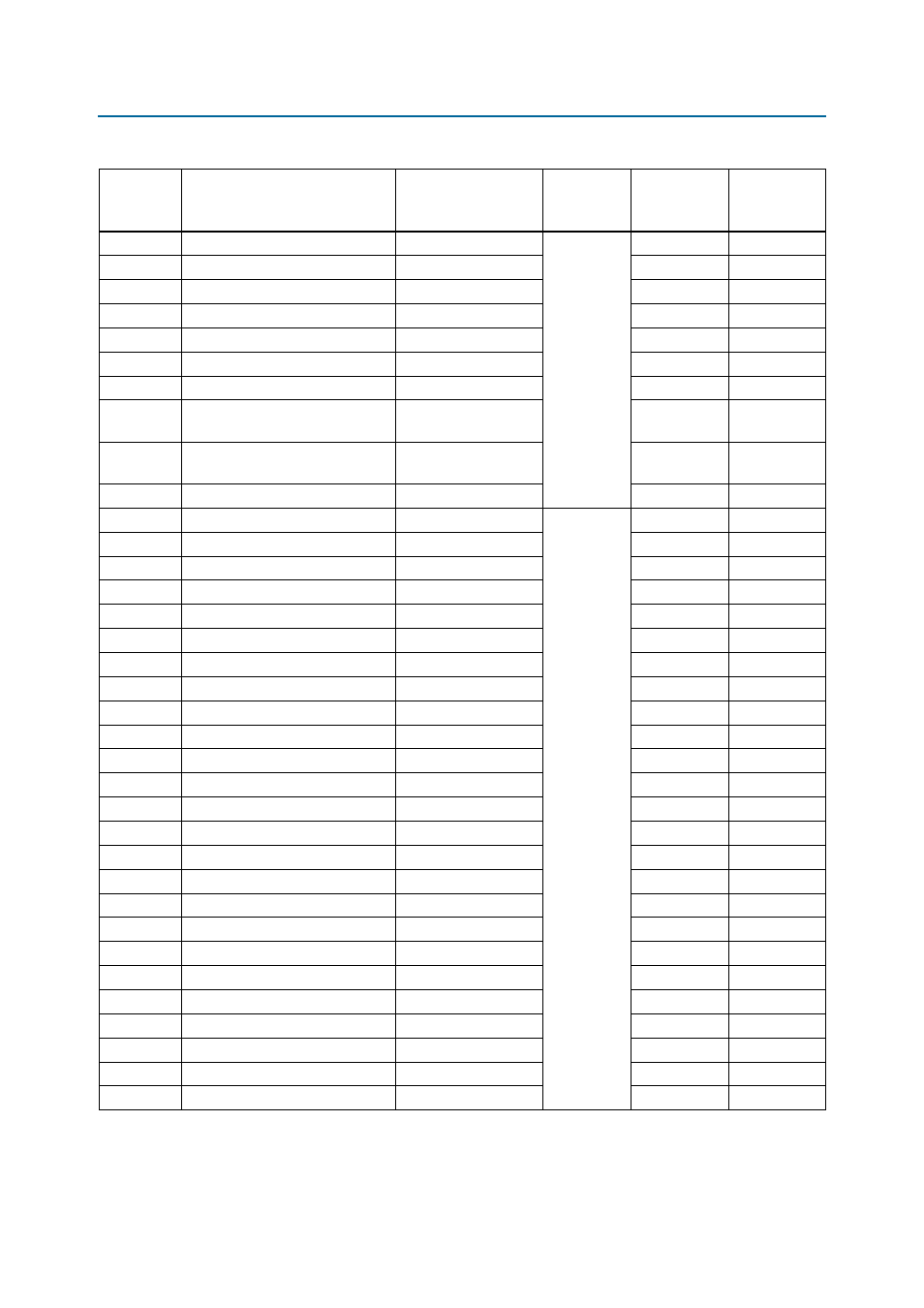

Table 2–34. HSMC Port B Pin Assignments, Schematic Signal Names, and Functions (Part 4 of 5)

Board

Reference

Description

Schematic Signal

Name

I/O Standard

Cyclone IV GX

Device

Pin Number

Other

Connections