Ddr2 sdram bottom port, Ddr2 sdram bottom port –41 – Altera Cyclone IV GX FPGA Development Board User Manual

Page 49

Chapter 2: Board Components

2–41

Memory

May 2013

Altera Corporation

Cyclone IV GX FPGA Development Board

Reference Manual

DDR2 SDRAM Bottom Port

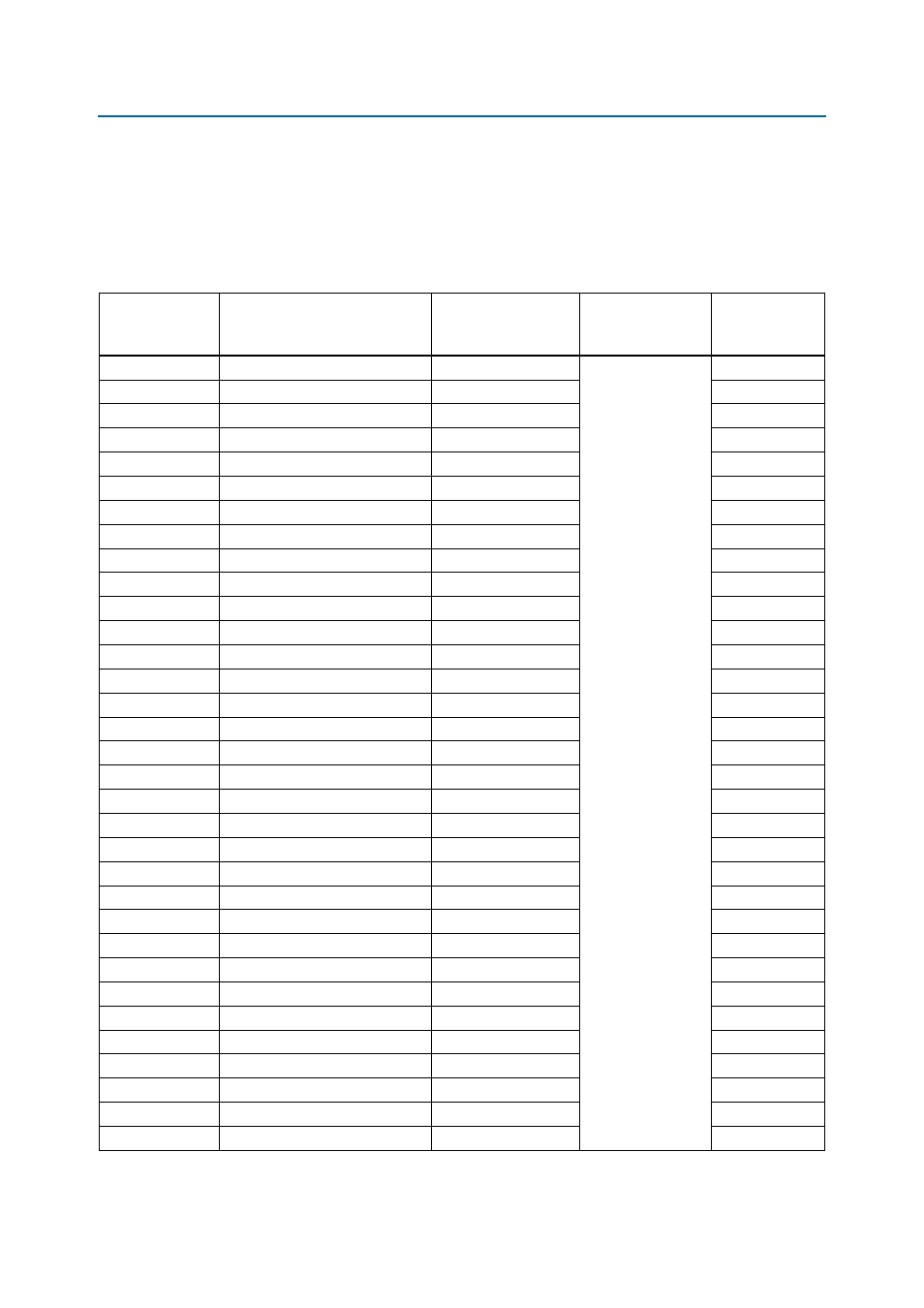

The DDR2 SDRAM bottom port consists of two DDR2 devices (U17 and U19).

lists the DDR2 bottom port pin assignments, signal names, and its

functions. The signal names and types are relative to the Cyclone IV GX device in

terms of I/O setting and direction.

Table 2–38. DDR2 SDRAM Bottom Port Pin Assignments, Signal Names and Functions (Part 1 of 2)

Board Reference

Description

Schematic Signal

Name

I/O Standard

Cyclone IV GX

Device

Pin Number

U17.R2, U19.R2

Address bus

DDR2B_A12

1.8-V SSTL Class I

AB11

U17.P7, U19.P7

Address bus

DDR2B_A11

AE15

U17.M2, U19.M2

Address bus

DDR2B_A10

AH8

U17.P3, U19.P3

Address bus

DDR2B_A9

AG7

U17.P8, U19.P8

Address bus

DDR2B_A8

AA16

U17.P2, U19.P2

Address bus

DDR2B_A7

AG8

U17.N7, U19.N7

Address bus

DDR2B_A6

AH14

U17.N3, U19.N3

Address bus

DDR2B_A5

AK7

U17.N8, U19.N8

Address bus

DDR2B_A4

AG15

U17.N2, U19.N2

Address bus

DDR2B_A3

AH7

U17.M7, U19.M7

Address bus

DDR2B_A2

AB14

U17.M3, U19.M3

Address bus

DDR2B_A1

AK9

U17.M8, U19.M8

Address bus

DDR2B_A0

AG14

U17.L3, U19.L3

Bank address bus

DDR2B_BA1

AJ9

U17.L2, U19.L2

Bank address bus

DDR2B_BA0

AA12

U17.K7, U19.K7

Row address select

DDR2B_RASn

AG12

U17.L7, U19.L7

Column address select

DDR2B_CASn

AK10

U17.L8, U19.L8

Chip select

DDR2B_CSn

AK12

U17.K3, U19.K3

Write enable

DDR2B_WEn

AH10

U17.K9, U19.K9

Termination enable

DDR2B_ODT

AF13

U17.K2, U19.K2

Clock enable

DDR2B_CKE

AA13

U17.J8, U19.J8

Clock P

DDR2B_CLK_P

AF4

U17.K8, U19.K8

Clock N

DDR2B_CLK_N

AG4

U19.G8,

Data bus byte lane 0

DDR2B_DQ0

AG5

U19.G2

Data bus byte lane 0

DDR2B_DQ1

AJ3

U19.H7

Data bus byte lane 0

DDR2B_DQ2

AK4

U19.H3

Data bus byte lane 0

DDR2B_DQ3

AJ4

U19.H1

Data bus byte lane 0

DDR2B_DQ4

AH2

U19.H9

Data bus byte lane 0

DDR2B_DQ5

AH6

U19.F1

Data bus byte lane 0

DDR2B_DQ6

AF3

U19.F9

Data bus byte lane 0

DDR2B_DQ7

AK5

U19.F3

Write mask byte lane 0

DDR2B_DM0

AE3

U19.F7

Data strobe byte lane 0

DDR2B_DQS0

AD9