23 cavium 2 c_mul clock divisor control, Table 5-23, Cavium 1 c_mull clock divisor control (0x70) – Artesyn ATCA-9305 User's Manual (May 2014) User Manual

Page 121: Table 5-24, Cavium 2 c_mull clock divisor control (0x74), Management processor cpld

Management Processor CPLD

ATCA-9305 User’s Manual (10009109-07)

121

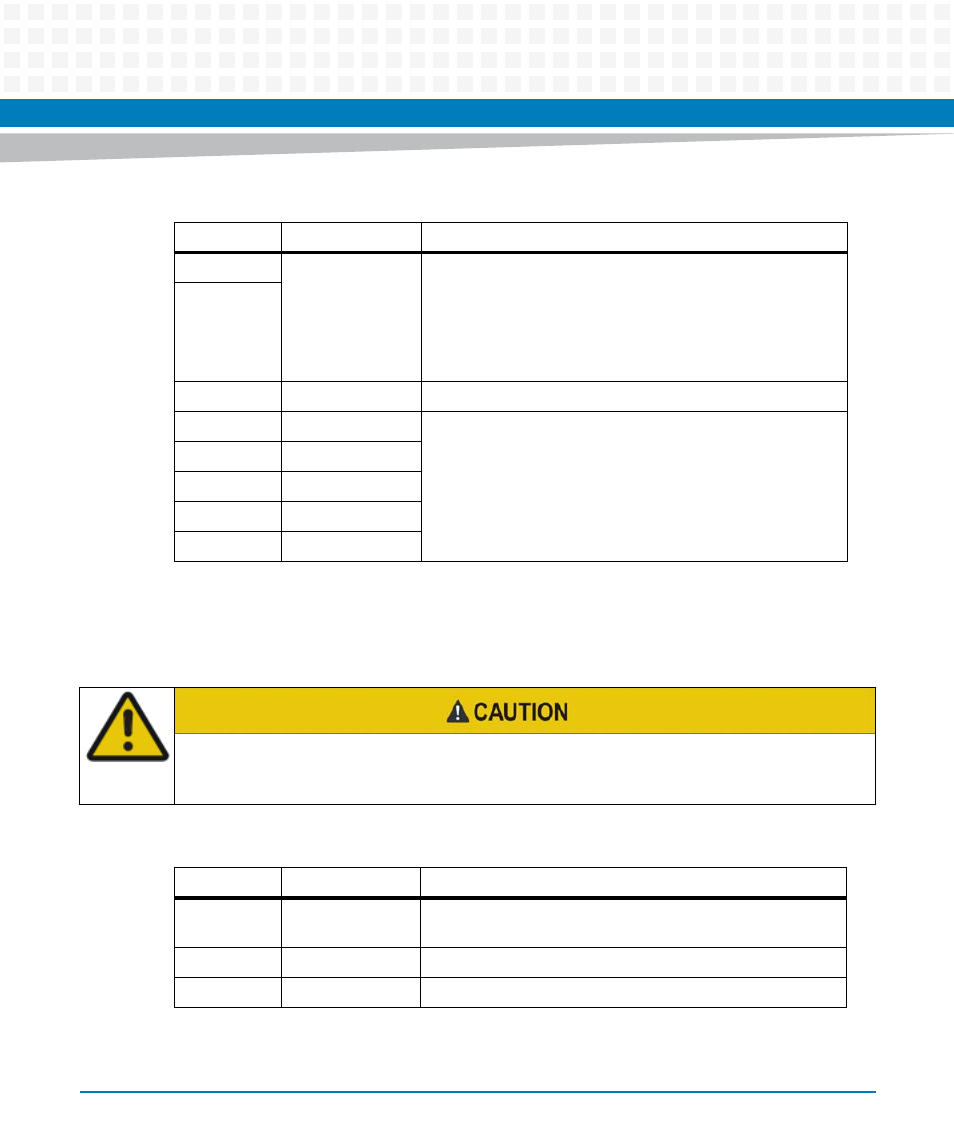

5.1.23 Cavium 2 C_MUL Clock Divisor Control

Use the C_MUL2 register to reduce the speed of the Cavium CN5860 processor 2 core.

Table 5-23 Cavium 1 C_MULL Clock Divisor Control (0x70)

Bits

Function

Description

7

CAVF

Cavium Frequency resistor set bit (read-only)

00 600

01 750

10 800

11 reserved

6

5

CMULOE

C_MUL Output Enable

4

P1CMUL4

These bits drive directly to the Cavium 1. The core clock

speed is the number multiplied by 50 MHz. For example, the

800 MHz core is set to 16(0x10).

3

P1CMUL3

2

P1CMUL2

1

P1CMUL1

0

P1CMUL0

Do not over-clock the Cavium frequency (bits 6:7 hard strapped).

Table 5-24 Cavium 2 C_MULL Clock Divisor Control (0x74)

Bits

Function

Description

7

CAVF1

Cavium 1 Frequency resistor set bit (read-only, see

6

CAVF0

Cavium 0 Frequency resistor set bit (read-only)

5

CMULOE

C_MUL Output Enable