Table 4-2, Mpc8548 address summary, Management complex – Artesyn ATCA-9305 User's Manual (May 2014) User Manual

Page 95

Management Complex

ATCA-9305 User’s Manual (10009109-07)

95

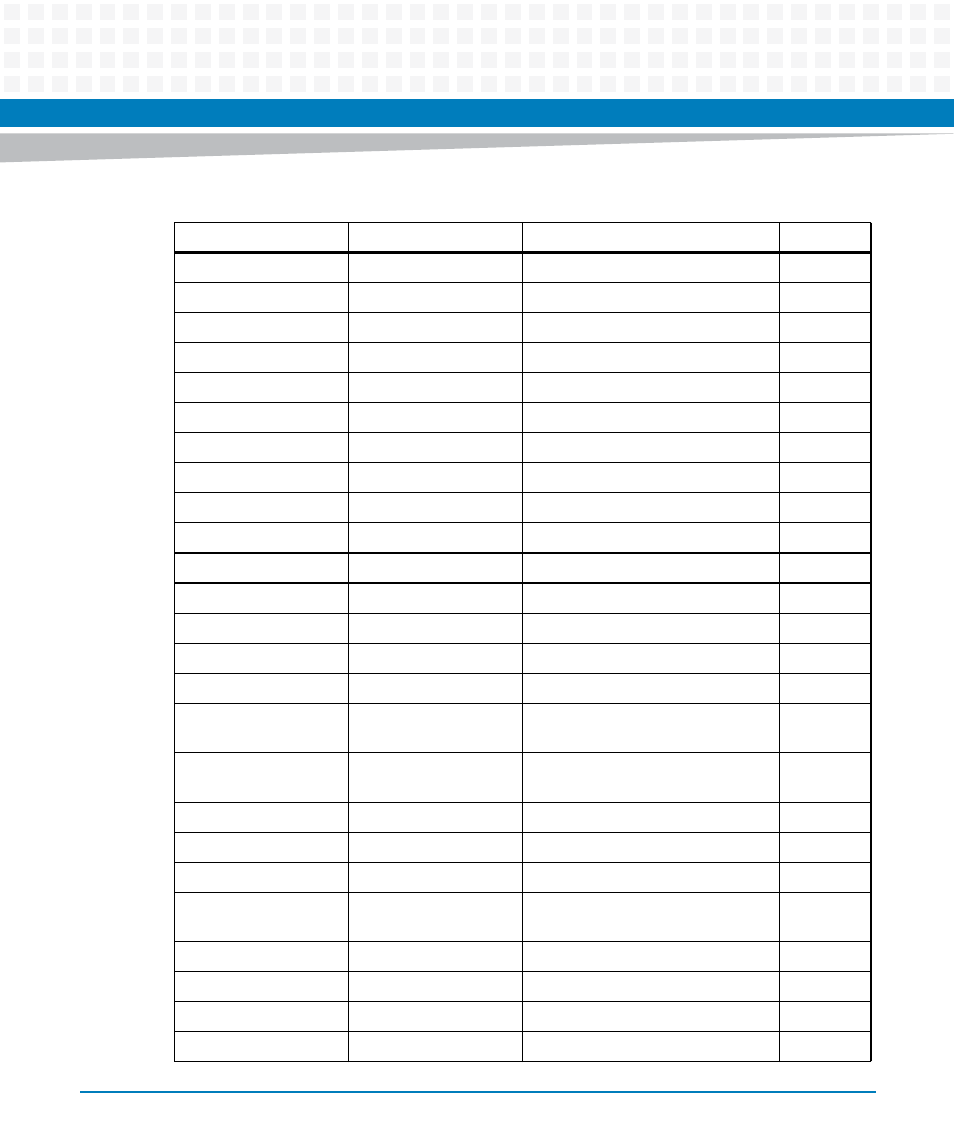

Table 4-2 MPC8548 Address Summary

Hex Physical Address

Access Mode

Register Description

See Page

FFF8,0000

R/W

Boot window (512 KB)

–

FF80.0000

-

reserved (7.5 MB)

FF70,0000

R/W

MPC8548 CCSRBAR (1MB)

–

FC88,0000

–

reserved (46 MB)

FC80,0000

R/W

Socketed flash, optional (512 KB)

FC48,0000

–

reserved (3.5 MB)

FC40,00DC0

R/W

Serial IRQ Interrupt 2

FC40,00D8

R/W

Serial IRQ Interrupt 1

FC40,00D4

R/W

LPC Data

FC40,00D0

R/W

Low Pin Count (LPC) Bus Control

FC40,008C

R/W

IPMP/IPMC GPIO Control

FC40,0088

R/W

Cavium GPIO Data Input

FC40,0084

R/W

Cavium GPIO Data Output

FC40,0080

R/W

Cavium GPIO Control

FC40,0078

R/W

Altera JTAG Chain Software Control

FC40,0074

R/W

Cavium 2 C_MUL Clock Divisor

Control

FC40,0070

R/W

Cavium 1 C_MUL Clock Divisor

Control

FC40,0068

R/W

RTM Control

FC40,0064

R/W

RTM GPIO Control

FC40,0060

R/W

RTM GPIO State

FC40,0054

R/W

Miscellaneous Control (SIO, I2C,

Test Clock)

FC40,0050

R/W

Boot Device Redirection

FC40,0040

R/W

Scratch #1

-

FC40,003C

R/W

Reset Command Sticky #2

FC40,0038

R/W

Reset Command Sticky #1