23 ipmc headers, Table 7-52, Ipmp cpld jp1 pin assignments – Artesyn ATCA-9305 User's Manual (May 2014) User Manual

Page 211: Table 7-53, Ipmp eia-232 p4 pin assignments, System management

System Management

ATCA-9305 User’s Manual (10009109-07)

211

Preparation

This step erases the region in the flash memory where the component image will be written.

Component Upload

This step is designed to upload the component image via IPMB or payload interface and write

it into the flash memory.

Component Activation

This step activates the previously upgraded component. This step can be deferred and

performed later. For more details, refer to the HPM.1 specification listed in

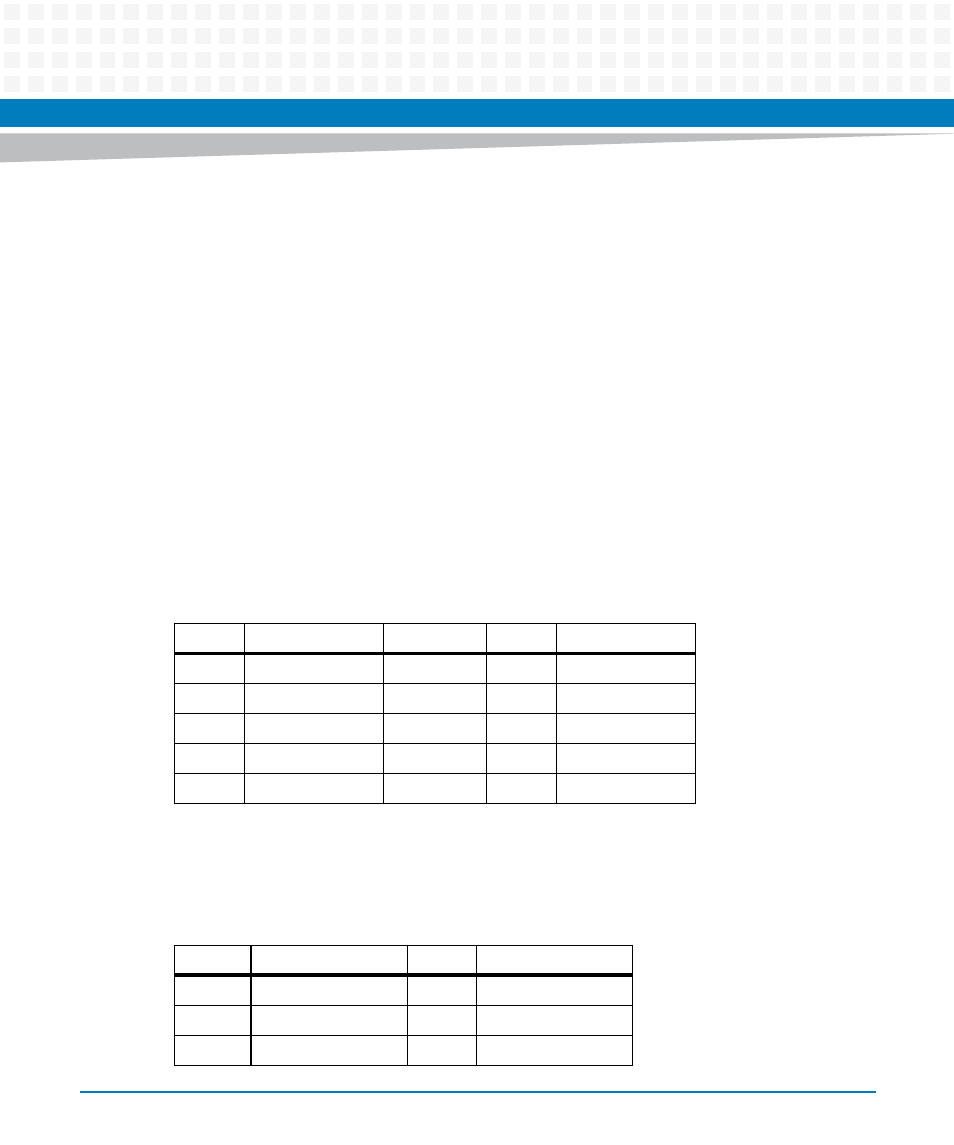

7.23 IPMC Headers

This JTAG header (JP1) is available for in-system programming of the CPLD.

The EIA-232 debug serial port is accessible via the mini-B USB connector P4. Default port

settings are: 115200 baud (optional 9600), 8 data bits, 1 stop bit, no parity, no flow control.

Table 7-52 IPMP CPLD JP1 Pin Assignments

Pin

Signal

Direction

Pin

Signal

1

CPLD_TCK

out

2

ground

3

CPLD_TDI

in

4

3_3V (fused)

5

CPLD_TMS

out

6

no connect

7

no connect

-

8

no connect

9

CPLD_TDO

out

10

ground

Table 7-53 IPMP EIA-232 P4 Pin Assignments

Pin

Signal

Pin

Signal

1

no connect

2

IPMP_RS_232_Rx

3

IPMP_RS_232_Tx

4

no connect

5

ground

6

ground