1588v2 interfaces, Ieee 1588v2 egress transmit signals, 1588v2 interfaces -18 – Altera Low Latency Ethernet 10G MAC User Manual

Page 100: Ieee 1588v2 egress transmit signals -18

Signal

Direction

Width

Description

mii_rx_d[]

Out

4

RX data bus.

mii_rx_dv

Out

1

When asserted, indicates the RX data is valid.

mii_rx_err

Out

1

When asserted, indicates the RX data contains

error.

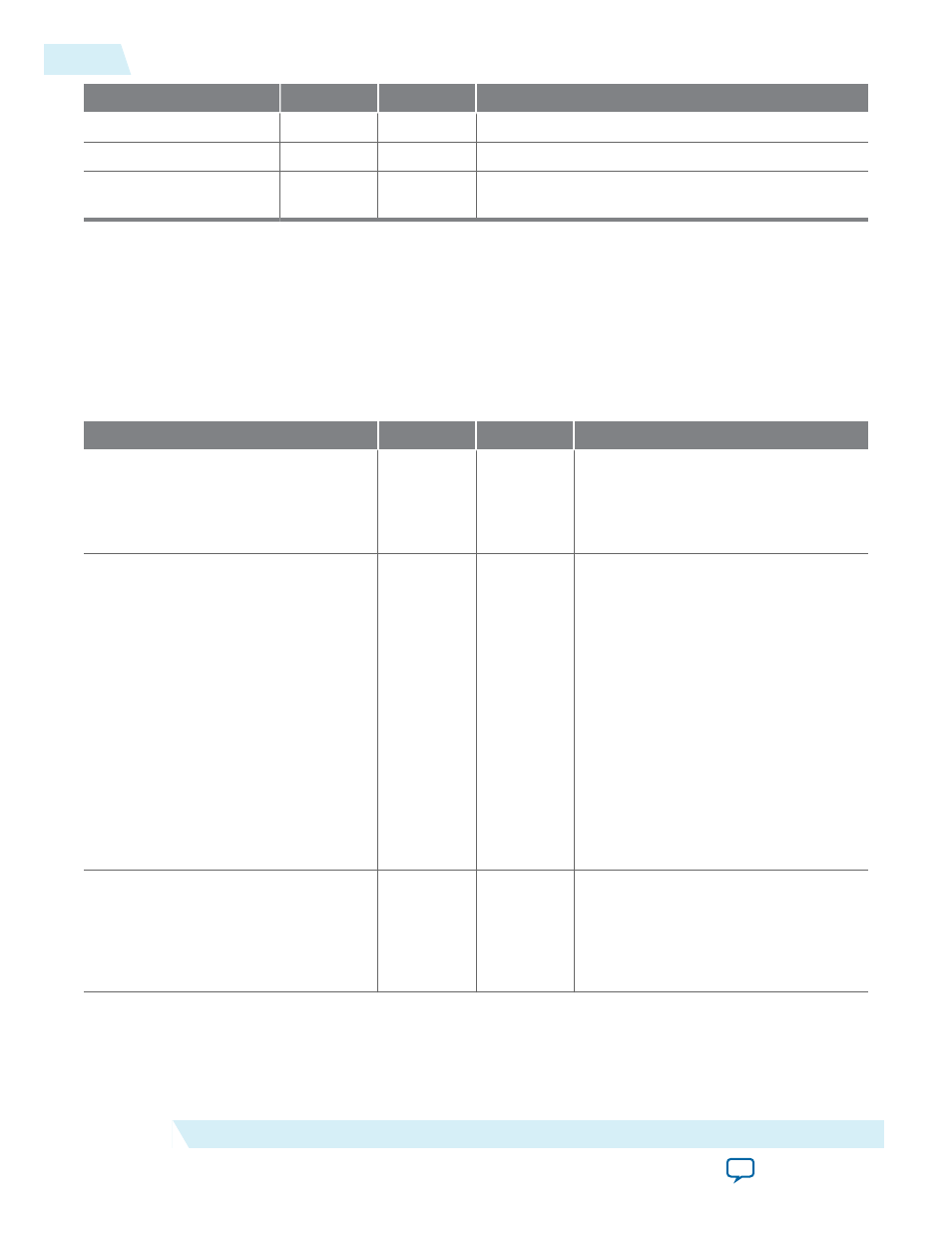

1588v2 Interfaces

IEEE 1588v2 Egress Transmit Signals

The signals below are present when you select the Enable time stamping option.

Table 5-17: IEEE 1588v2 Egress Transmit Signals

Signal

Direction

Width

Description

tx_egress_timestamp_request_

valid

In

1

Assert this signal to request for a

timestamp for the transmit frame.

This signal must be asserted in the

same clock cycle

avalon_st_tx_

startofpacket

is asserted.

tx_egress_timestamp_request_

fingerprint[]

In

n

n = value of the Timestamp

fingerprint width parameter.

Use this bus to specify the fingerprint

of the transmit frame that you are

requesting a timestamp for. This bus

must carry a valid fingerprint at the

same time

tx_egress_timestamp_

request_valid

is asserted.

The purpose of the fingerprint is to

associate the timestamp with the

packet. Thus, it can be the sequence

ID field from the PTP packet or some

other unique field of the packet, to

validate both the fingerprint and

timestamp collected from the CPU.

tx_egress_timestamp_96b_valid

Out

1

When asserted, this signal qualifies

the timestamp on

tx_egress_

timestamp_96b_data[]

for the

transmit frame whose fingerprint is

specified by

tx_egress_timestamp_

96b_fingerprint[]

.

5-18

1588v2 Interfaces

UG-01144

2014.12.15

Altera Corporation

Interface Signals for LL Ethernet 10G MAC